- 您現在的位置:買賣IC網 > PDF目錄376430 > uPD750066GTA (NEC Corp.) CONNECTOR ACCESSORY PDF資料下載

參數資料

| 型號: | uPD750066GTA |

| 廠商: | NEC Corp. |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | 連接器附件 |

| 文件頁數: | 53/82頁 |

| 文件大小: | 460K |

| 代理商: | UPD750066GTA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

53

μ

PD750064, 750066, 750068, 750064(A), 750066(A), 750068(A)

Data Sheet U10165EJ2V0DS00

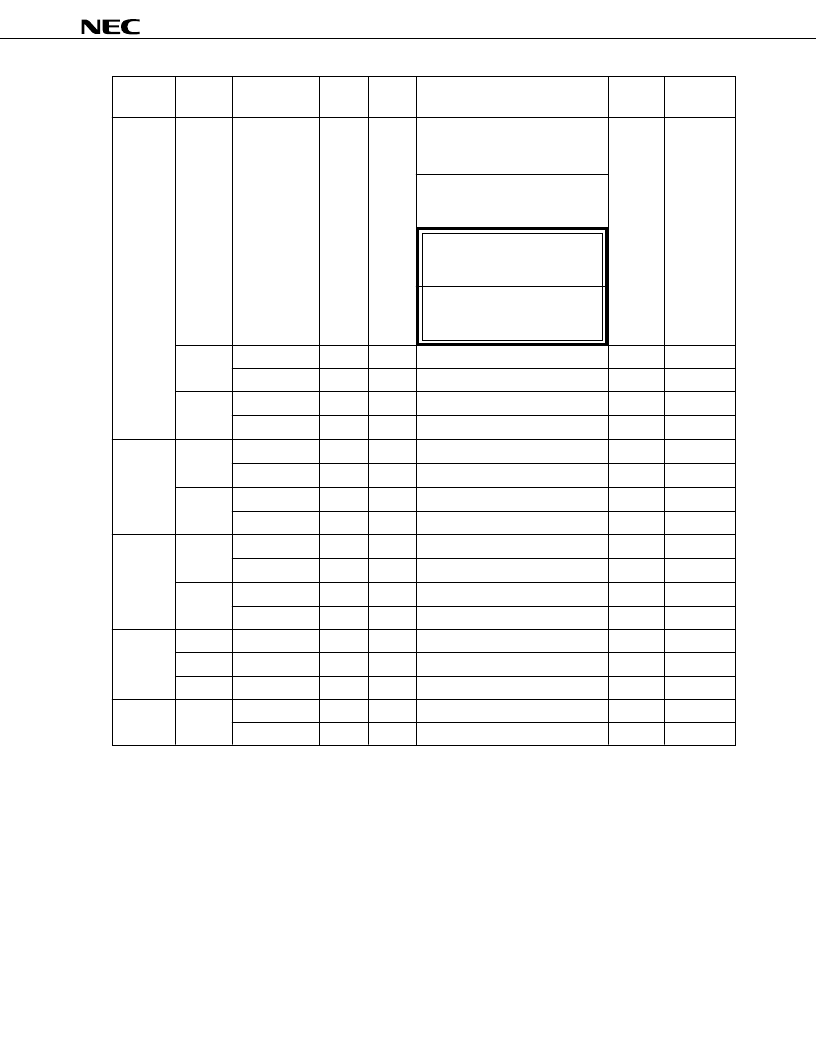

Instruction

Group

Number

of Bytes

Number

of Machine

Cycles

Addressing

Area

Mnemonic

Operand

Operation

Skip Condition

Subroutine

stack control

RETI

Note 1

1

3

μ

PD750064

MBE, RBE, 0, 0

←

(SP+1)

PC

11–0

←

(SP) (SP+3) (SP+2)

PSW

←

(SP+4) (SP+5), SP

←

SP+6

μ

PD750066, 750068

MBE, RBE, 0, PC

12

←

(SP+1)

PC

11–0

←

(SP) (SP+3) (SP+2)

PSW

←

(SP+4) (SP+5), SP

←

SP+6

μ

PD750064

0, 0, 0, 0

←

(SP+1)

PC

11–0

←

(SP) (SP+3) (SP+2)

PSW

←

(SP+4) (SP+5), SP

←

SP+6

μ

PD750066, 750068

0, 0, 0, PC

12

←

(SP+1)

PC

11–0

←

(SP) (SP+3) (SP+2)

PSW

←

(SP+4) (SP+5), SP

←

SP+6

PUSH

rp

1

1

(SP–1)(SP–2)

←

rp, SP

←

SP–2

BS

2

2

(SP–1)

←

MBS, (SP–2)

←

RBS, SP

←

SP–2

POP

rp

1

1

rp

←

(SP+1) (SP), SP

←

SP+2

BS

2

2

MBS

←

(SP+1), RBS

←

(SP), SP

←

SP+2

Interrupt

control

EI

2

2

IME (IPS.3)

←

1

IE

×××

2

2

IE

×××

←

1

DI

2

2

IME (IPS.3)

←

0

IE

×××

2

2

IE

×××

←

0

Input/output

IN

Note 2

A, PORTn

2

2

A

←

PORTn

(n = 0-6, 11)

XA, PORTn

2

2

XA

←

PORTn+1, PORTn

(n = 4)

OUT

Note 2

PORTn, A

2

2

PORTn

←

A

(n = 2-6)

PORTn, XA

2

2

PORTn+1, PORTn

←

XA

(n = 4)

CPU control

HALT

2

2

Set HALT Mode (PCC.2

←

1)

STOP

2

2

Set STOP Mode (PCC.3

←

1)

NOP

1

1

No Operation

Special

SEL

RBn

2

2

RBS

←

n

(n = 0-3)

MBn

2

2

MBS

←

n

(n = 0, 1, 15)

Notes 1.

The operations indicated with thick lines can be performed only in the Mk II mode. The other operations

can be performed only in the Mk I mode.

While the IN instruction and OUT instruction are being executed, the MBE must be set to 0 or 1, and

MBS must be set to 15.

2.

相關PDF資料 |

PDF描述 |

|---|---|

| UPD750064 | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750064CU | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750064CUA | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750064GT | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| uPD750066GT | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UPD750068GT-396 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。