- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384043 > UPD44324182F5-E37-EQ2-A (NEC Corp.) 36M-BIT DDRII SRAM 2-WORD BURST OPERATION PDF資料下載

參數(shù)資料

| 型號(hào): | UPD44324182F5-E37-EQ2-A |

| 廠商: | NEC Corp. |

| 元件分類: | DRAM |

| 英文描述: | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| 中文描述: | 36M條位SRAM的2條DDRII字爆發(fā)運(yùn)作 |

| 文件頁(yè)數(shù): | 10/40頁(yè) |

| 文件大小: | 361K |

| 代理商: | UPD44324182F5-E37-EQ2-A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

10

Data Sheet M16780EJ3V0DS

μ

PD44324082, 44324092, 44324182, 44324362

Power-on Sequence

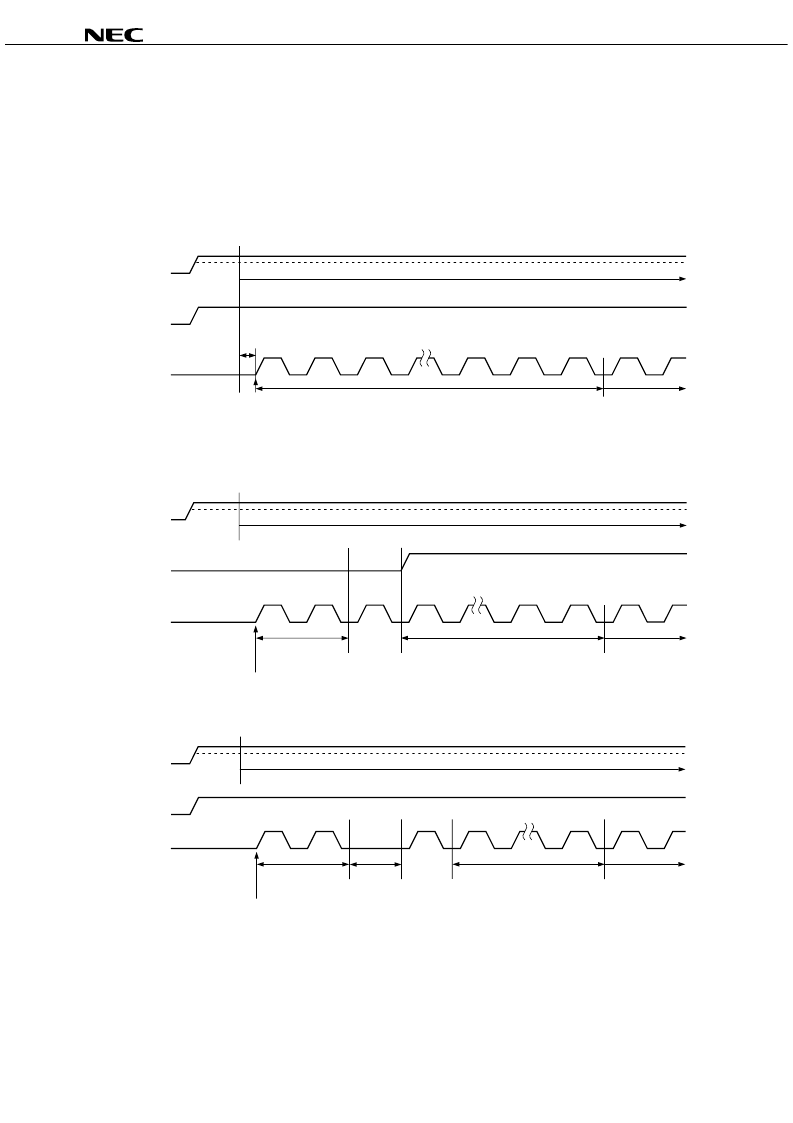

The following two timing charts show the recommended power-on sequence, i.e., when starting the clock after

V

DD

/V

DD

Q stable and when starting the clock before V

DD

/V

DD

Q stable.

1. Clock starts after V

DD

/V

DD

Q stable

The clock is supplied from a controller.

(a)

V

DD

/V

DD

Q

V

DD

/V

DD

Q Stable (<

±

0.1 V DC per 50 ns)

DLL#

Clock Start

Normal Operation

Start

Clock

Fix high (or tied to V

DD

Q)

20 ns (MIN.)

1,024 cycles or more

Stable Clock

Note

Note

Input a stable clock from the start.

(b)

V

DD

/V

DD

Q

DLL#

Switched to high after Clock is stable.

Unstable Clock

(level, frequency)

V

DD

/V

DD

Q Stable (<

±

0.1 V DC per 50 ns)

Clock

Clock Start

Normal Operation

Start

1,024 cycles or more

Stable Clock

(c)

V

DD

/V

DD

Q

DLL#

30 ns. (MIN.)

Clock Stop

V

DD

/V

DD

Q Stable (<

±

0.1 V DC per 50 ns)

Fix high (or tied to V

DD

Q)

Unstable Clock

(level, frequency)

Clock

Clock Start

Normal Operation

Start

1,024 cycles or more

Stable Clock

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD44324182F5-E40-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324182F5-E50-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324362F5-E37-EQ2 | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324362F5-E37-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324362F5-E40-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD44324185BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:SRAM Chip Sync Dual 1.8V 36M-Bit 2M x 18 0.45ns 165-Pin BGA 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324362BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324362BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324365BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324365BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。