- 您現在的位置:買賣IC網 > PDF目錄382627 > TMX320R2812ZHHS (Texas Instruments, Inc.) TMS320R2811, TMS320R2812 Digital Signal Processors PDF資料下載

參數資料

| 型號: | TMX320R2812ZHHS |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | TMS320R2811, TMS320R2812 Digital Signal Processors |

| 中文描述: | TMS320R2811,TMS320R2812數字信號處理器 |

| 文件頁數: | 113/147頁 |

| 文件大?。?/td> | 2021K |

| 代理商: | TMX320R2812ZHHS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁當前第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁

Electrical Specifications

113

June 2004

SPRS257

If the XREADY signal is sampled in the Synchronous mode (USEREADY = 1, READYMODE = 0), then:

LR

≥

t

c(XTIM)

LW

≥

t

c(XTIM)

2.

Active:

AR

≥

2 x t

c(XTIM)

AW

≥

2 x t

c(XTIM)

NOTE

: Restriction does not include external hardware wait states

1.

Lead:

These requirements result in the following XTIMING register configuration restrictions

:

XRDLEAD

≥

1

No hardware to detect illegal XTIMING configurations

XRDACTIVE

≥

1

XRDTRAIL

≥

0

XWRLEAD

≥

1

XWRACTIVE

≥

1

XWRTRAIL

≥

0

X2TIMING

0, 1

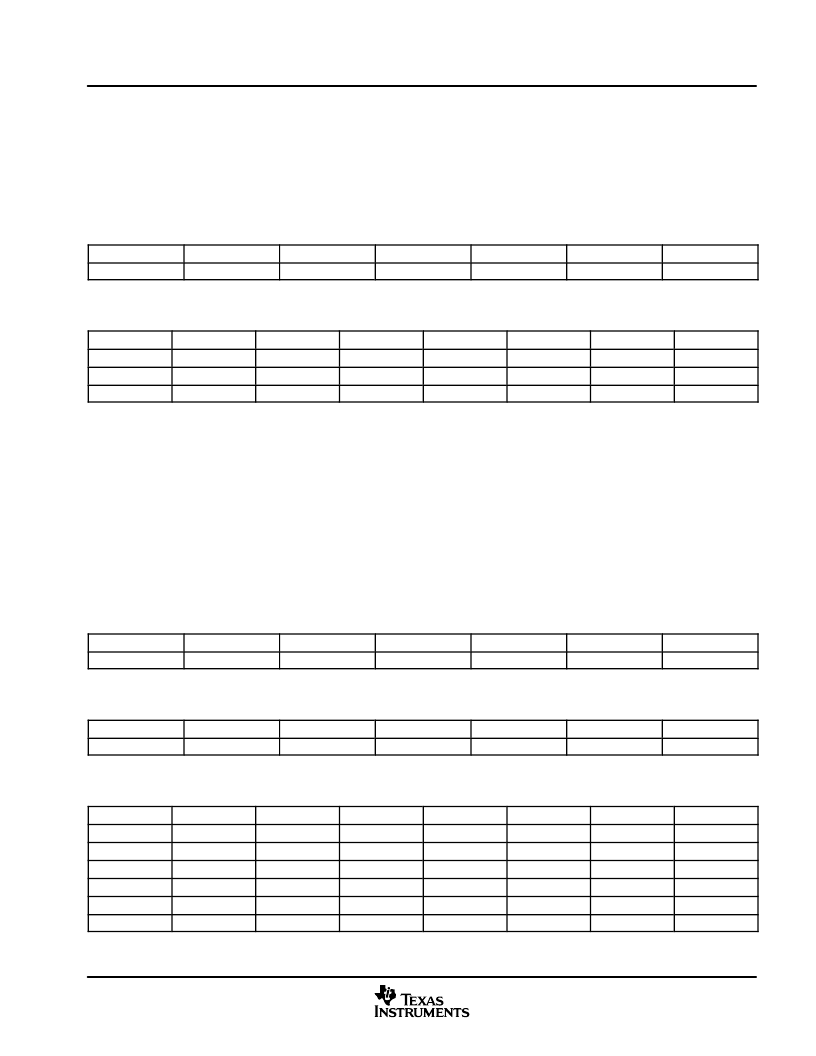

Examples of valid and invalid timing when using Synchronous XREADY

:

XRDLEAD

0

1

1

XRDACTIVE

0

0

1

XRDTRAIL

0

0

0

XWRLEAD

0

1

1

XWRACTIVE

0

0

1

XWRTRAIL

0

0

0

X2TIMING

0, 1

0, 1

0, 1

Invalid

Invalid

Valid

No hardware to detect illegal XTIMING configurations

If the XREADY signal is sampled in the Asynchronous mode (USEREADY = 1, READYMODE = 1), then:

LR

≥

t

c(XTIM)

LW

≥

t

c(XTIM)

2.

Active:

AR

≥

2 x t

c(XTIM)

AW

≥

2 x t

c(XTIM)

NOTE

: Restriction does not include external hardware wait states

LR + AR

≥

4 x t

c(XTIM)

LW + AW

≥

4 x t

c(XTIM)

NOTE

: Restriction does not include external hardware wait states

1.

Lead:

3.

Lead + Active:

These requirements result in the following XTIMING register configuration restrictions

:

XRDLEAD

≥

1

No hardware to detect illegal XTIMING configurations

or

XRDACTIVE

≥

2

XRDTRAIL

0

XWRLEAD

≥

1

XWRACTIVE

≥

2

XWRTRAIL

0

X2TIMING

0, 1

XRDLEAD

≥

2

No hardware to detect illegal XTIMING configurations

XRDACTIVE

≥

1

XRDTRAIL

0

XWRLEAD

≥

2

XWRACTIVE

≥

1

XWRTRAIL

0

X2TIMING

0, 1

Examples of valid and invalid timing when using Asynchronous XREADY

:

XRDLEAD

0

1

1

1

1

2

XRDACTIVE

0

0

1

1

2

1

XRDTRAIL

0

0

0

0

0

0

XWRLEAD

0

1

1

1

1

2

XWRACTIVE

0

0

1

1

2

1

XWRTRAIL

0

0

0

0

0

0

X2TIMING

0, 1

0, 1

0

1

0, 1

0, 1

Invalid

Invalid

Invalid

Valid

Valid

Valid

No hardware to detect illegal XTIMING configurations

A

相關PDF資料 |

PDF描述 |

|---|---|

| TMP320R2811ZHHA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320R2811ZHHQ | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320R2811ZHHS | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320R2812GHHA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320R2812GHHQ | TMS320R2811, TMS320R2812 Digital Signal Processors |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMX320TCI100BGLZ7 | 制造商:Texas Instruments 功能描述: |

| TMX320TCI100GLZ | 制造商:Texas Instruments 功能描述: |

| TMX320TCI100ZLZ6 | 制造商:Texas Instruments 功能描述: |

| TMX320TCI100ZLZ6N | 制造商:Texas Instruments 功能描述: |

| TMX320TCI100ZLZ7N | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。