- 您現(xiàn)在的位置:買賣IC網 > PDF目錄383960 > TMX320C6411GLZ (Texas Instruments, Inc.) FIXED POINT DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號: | TMX320C6411GLZ |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 定點數(shù)字信號處理器 |

| 文件頁數(shù): | 40/119頁 |

| 文件大?。?/td> | 1742K |

| 代理商: | TMX320C6411GLZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁

SPRS196H MARCH 2002 REVISED JULY 2004

40

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

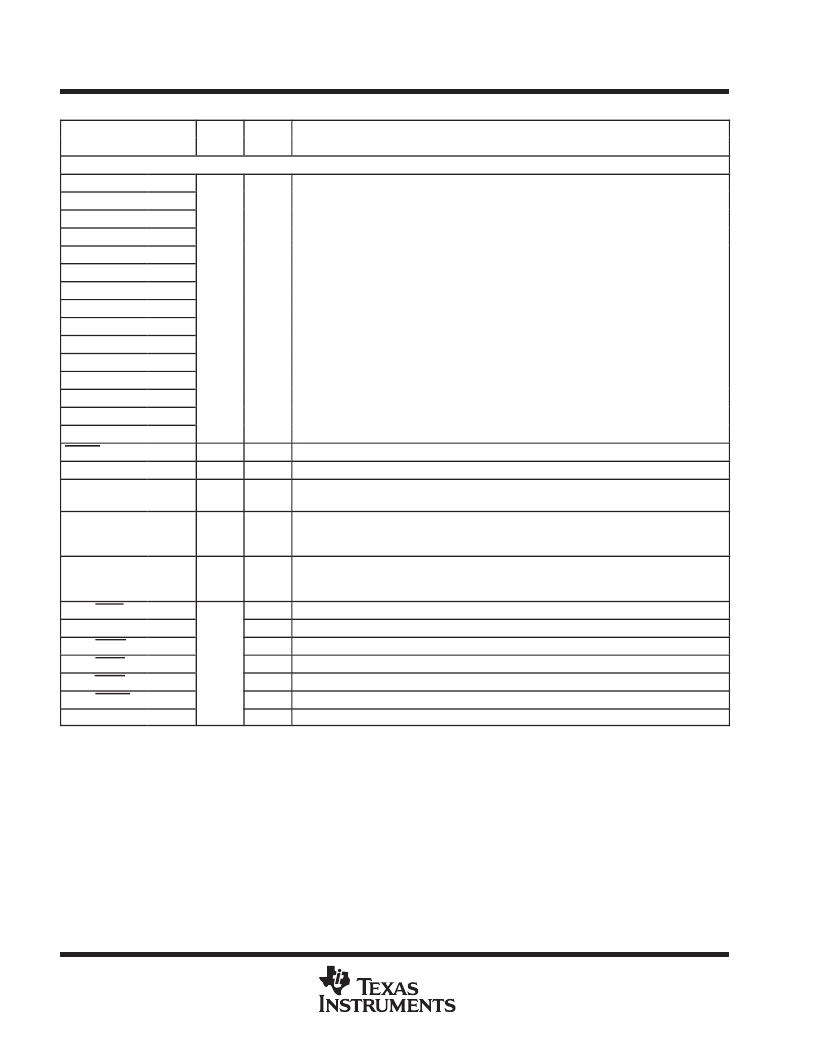

Terminal Functions (Continued)

SIGNAL

TYPE

IPD/

IPU

DESCRIPTION

NAME

NO.

HOST-PORT INTERFACE (HPI) or PERIPHERAL COMPONENT INTERCONNECT (PCI) (CONTINUED)

U1

HD14/AD14§

HD13/AD13§

HD12/AD12§

HD11/AD11§

HD10/AD10§

HD9/AD9§

HD8/AD8§

HD7/AD7§

HD6/AD6§

HD5/AD5§

HD4/AD4§

HD3/AD3§

HD2/AD2§

HD1/AD1§

HD0/AD0§

PCBE0§

U3

Host-port data (

I/O/Z

) [default] or PCI data-address bus (

I/O/Z

)

U2

V4

Used for transfer of data, address, and control

resistor

Host-Port bus width (HPI_WIDTH) user-configurable at device reset via a 10-k

pullup/pulldown resistor on the HD5 pin:

V1

As HPI data bus (PCI_EN pin = 0)

V3

V2

HD5 pin = 0: HPI operates as an HPI16.

(HPI bus is 16 bits wide. HD[15:0] pins are used and the remaining HD[31:16] pins are

reserved pins in the high-impedance state.)

W2

I/O/Z

W4

Y1

HD5 pin = 1: HPI operates as an HPI32.

(HPI bus is 32 bits wide. All HD[31:0] pins are used for host-port operations.)

Y3

Y2

Y4

As PCI data-address bus (PCI_EN pin = 1)

Used for transfer of data and address

AA1

AA3

W3

I/O/Z

PCI command/byte enable 0 (

I/O/Z

). When PCI is disabled (PCI_EN = 0), this pin is tied-off.

XSP_CS

AD1

O

IPD

PCI serial interface chip select (

O

). When PCI is disabled (PCI_EN = 0), this pin is tied-off.

XSP_CLK

AC2

I/O/Z

IPD

This pin has no function at default [default] or when PCI is enabled (PCI_EN = 1), this pin is the

PCI serial interface clock (

O

).

XSP_DI

AB3

I

IPU

This pin has no function at default [default] or when PCI is enabled (PCI_EN = 1), this pin is the

PCI serial interface data in (

I

). In PCI mode, this pin is connected to the output data pin of the

serial PROM.

XSP_DO

AA2

O/Z

IPU

This pin has no function at default [default] or when PCI is enabled (PCI_EN = 1), this pin is the

PCI serial interface data out (

O

). In PCI mode, this pin is connected to the input data pin of the

serial PROM.

GP15/PRST§

GP14/PCLK§

GP13/PINTA§

GP12/PGNT§

GP11/PREQ§

GP10/PCBE3§

GP9/PIDSEL§

I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground

IPD = Internal pulldown, IPU = Internal pullup. (These IPD/IPU signal pins feature a 30-k

IPD or IPU resistor. To pull up a signal to the opposite

supply rail, a 1-k

resistor should be used, unless otherwise noted.)

§These pins are multiplexed pins. For more details, see the Device Configurations section of this data sheet.

G3

General-purpose input/output (GPIO) 15 pin (

I/O/Z

) or PCI reset (

I

). No function at default.

GPIO 14 pin (

I/O/Z

) or PCI clock (

I

). No function at default.

GPIO 13 pin (

I/O/Z

) or PCI interrupt A (

O/Z

). No function at default.

GPIO 12 pin (

I/O/Z

) or PCI bus grant (

I

). No function at default.

GPIO 11 pin (

I/O/Z

) or PCI bus request (

O/Z

). No function at default.

GPIO 10 pin (

I/O/Z

) or PCI command/byte enable 3 (

I/O/Z

). No function at default.

GPIO 9 pin (

I/O/Z

) or PCI initialization device select (

I

). No function at default.

F2

G4

J3

I/O/Z

F1

L2

M3

相關PDF資料 |

PDF描述 |

|---|---|

| TMX320C6411ZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMX32C6411AGLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMP32C6411AZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMP320C6411AZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMX32C6411AZLZ | ER 5C 2#6 3#4 SKT PLUG |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320C6411GLZ300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411GLZ5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411GLZA300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411GLZA5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411ZLZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED POINT DIGITAL SIGNAL PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。