- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382629 > TMP320R2811GHHA (Texas Instruments, Inc.) Aluminum Electrolytic Radial Lead Extremely Low Impedance Capacitor; Capacitance: 2700uF; Voltage: 6.3V; Case Size: 12.5x25 mm; Packaging: Bulk PDF資料下載

參數(shù)資料

| 型號(hào): | TMP320R2811GHHA |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Aluminum Electrolytic Radial Lead Extremely Low Impedance Capacitor; Capacitance: 2700uF; Voltage: 6.3V; Case Size: 12.5x25 mm; Packaging: Bulk |

| 中文描述: | TMS320R2811,TMS320R2812數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 47/147頁(yè) |

| 文件大?。?/td> | 2021K |

| 代理商: | TMP320R2811GHHA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)

Functional Overview

47

June 2004

SPRS257

Normally, when the input clocks are present, the watchdog counter will decrement to initiate a watchdog reset

or WDINT interrupt. However, when the external input clock fails, the watchdog counter will stop decrementing

(i.e., the watchdog counter does not change with the limp-mode clock). This condition could be used by the

application firmware to detect the input clock failure and initiate necessary shut-down procedure for the

system.

3.7.3

PLL-Based Clock Module

R281x has an on-chip, PLL-based clock module. This module provides all the necessary clocking signals for

the device, as well as control for low-power mode entry. The PLL has a 4-bit ratio control to select different

CPU clock rates. The watchdog module should be disabled before writing to the PLLCR register. It can be

re-enabled (if need be) after the PLL module has stabilized, which takes 131072 XCLKIN cycles.

The PLL-based clock module provides two modes of operation:

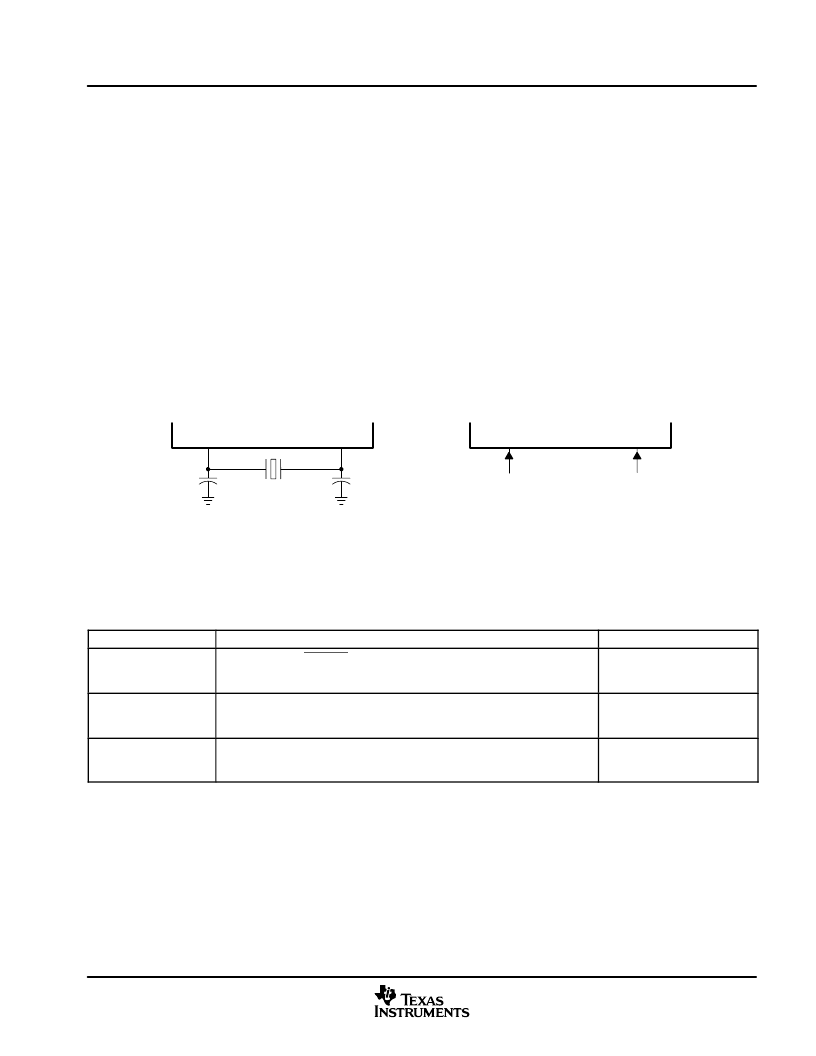

Crystal-operation

This mode allows the use of an external crystal/resonator to provide the time base to the device.

External clock source operation

This mode allows the internal oscillator to be bypassed. The device clocks are generated from an external

clock source input on the X1/XCLKIN pin.

External Clock Signal

(Toggling 0

V

DD

)

C

b1

(see Note A)

X2

X1/XCLKIN

X1/XCLKIN

X2

Crystal

(a)

C

b2

(see Note A)

(b)

NC

NOTE A: TI recommends that customers have the resonator/crystal vendor characterize the operation of their device with the DSP chip. The

resonator/crystal vendor has the equipment and expertise to tune the tank circuit. The vendor can also advise the customer regarding

the proper tank component values that will ensure start-up and stability over the entire operating range.

Figure 3

9. Recommended Crystal/Clock Connection

Table 3

13. Possible PLL Configuration Modes

PLL MODE

REMARKS

SYSCLKOUT

PLL Disabled

Invoked by tying XPLLDIS pin low upon reset. PLL block is completely

disabled. Clock input to the CPU (CLKIN) is directly derived from the clock

signal present at the X1/XCLKIN pin.

XCLKIN

PLL Bypassed

Default PLL configuration upon power-up, if PLL is not disabled. The PLL

itself is bypassed. However, the /2 module in the PLL block divides the clock

input at the X1/XCLKIN pin by two before feeding it to the CPU.

XCLKIN/2

PLL Enabled

Achieved by writing a non-zero value “n” into PLLCR register. The /2 module

in the PLL block now divides the output of the PLL by two before feeding it to

the CPU.

(XCLKIN * n) / 2

3.7.4

External Reference Oscillator Clock Option

The typical specifications for the external quartz crystal for a frequency of 30 MHz are listed below:

Fundamental mode, parallel resonant

C

L

(load capacitance) = 12 pF

C

L1

= C

L2

= 24 pF

C

shunt

= 6 pF

ESR range = 25 to 40

A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMR320F2811GHHA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMR320R2811GHHA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMR320R2812GHHS | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320F2812PBKS | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320F2812PGFQ | TMS320R2811, TMS320R2812 Digital Signal Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP34092PQL-64 | 制造商:Texas Instruments 功能描述: |

| TMP35FS | 制造商:Analog Devices 功能描述:Temp Sensor Analog(Voltage) Serial (2-Wire) 8-Pin SOIC N 制造商:Rochester Electronics LLC 功能描述:3V TEMPERATURE SENSOR - Bulk |

| TMP35FS-REEL | 制造商:Analog Devices 功能描述:Temp Sensor Analog Serial (2-Wire) 8-Pin SOIC N T/R 制造商:Rochester Electronics LLC 功能描述:3V TEMPERATURE SENSOR TAPE & REEL - Tape and Reel |

| TMP35FSZ | 制造商:Analog Devices 功能描述:Temperature Sensor IC |

| TMP35FSZ-REEL | 制造商:Analog Devices 功能描述:TEMP SENSOR ANLG SERL 8SOIC N - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。