- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄297500 > TLV320AIC22PTR (Texas Instruments, Inc.) DUAL VOIP CODEC PDF資料下載

參數(shù)資料

| 型號(hào): | TLV320AIC22PTR |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | Codec |

| 英文描述: | DUAL VOIP CODEC |

| 中文描述: | 雙VoIP編解碼器 |

| 文件頁數(shù): | 15/55頁 |

| 文件大?。?/td> | 763K |

| 代理商: | TLV320AIC22PTR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

TLV320AIC22

DUAL VOIP CODEC

SLAS281B – JULY 2000 – REVISED JUNE 2002

22

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

detailed description (continued)

control register address and data

When the I2C/SPI pin is tied to a logic low, the serial interface is selected for controlling the device. Control

information is sent and received in time slots 0 and 1. An active-high pulse on the FSYNC pin indicates the start

of a frame. The structure of time slots 0 and 1 is shown in Figures 5 and 6. Bit 15 (the MSB) is transmitted or

received first. Transmitted data is sent on the rising edge of BCLK and data being received is latched on the

falling edge of BCLK.

Time slot 0 indicates:

D If a read or write operation is occurring

D Which device is being accessed

D The register address within the device being accessed

AD0 (LSB) and AD1 (MSB) form the device address. Up to four TLV320AIC22 devices can be addressed, with

addresses ranging from 0 to 3. The five LSBs in time slot 0 are unused.

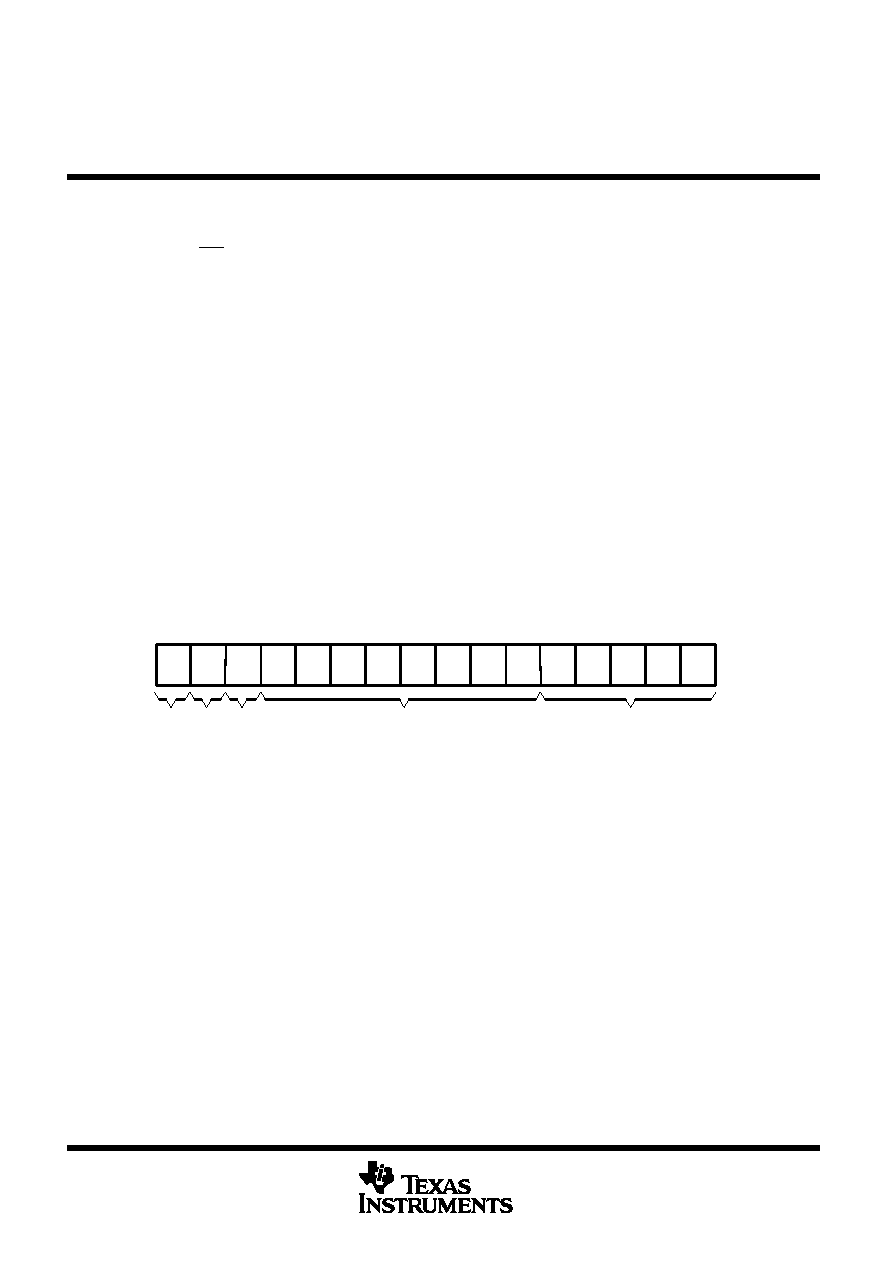

Slot 0:

B15

Read/write control

1 = Write, 0 = Read

B14

AD1 device address bit (MSB)

B13

AD0 device address bit (LSB)

B12–B5

Register address (8 bits)

B4–B0

Unused

0

1

87

6

5

4

3

2

10

11

12

13

14

15

9

R/W

AD1

AD0

Register Address

Unused

MSB

LSB

NOTE: The register address is the binary equivalent of the register number

Figure 5. Bit Assignment and Definition for Slot-0 Word

If bit 15 in slot 0 is a 1, a write operation has been requested by the DSP. The DSP drives data onto the DIN

pin in the next time slot (time slot 1) as follows:

D The 8 bits of data to be written into the register appear on the first 8 bits, with the MSB appearing first.

D The next 8 bits (8 LSBs) are unused.

If bit 15 in slot 0 is a 0 a read operation has been requested. The TLV320AIC22 compares the values of the

device address bits, bits 14 and 13 of time slot 0 (AD1 and AD0 bits) to the configuration of the AD1 and AD0

pins on the device to determine if it is the device being addressed. The device drives data on DOUT if it is the

addressed device, as follows:

D The 8 bits of data from the addressed register appear in the first 8 bits, with the MSB appearing first.

D The next 8 bits (8 LSBs) are unused.

Slot 1:

B15–B8

Control register data

B7–B0

Unused

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC26IRHBG4 | LOW POWER STEREO AUDIO CODEC WITH HEADPHONE/SPEAKER AMPLIFIER AND 12-BIT BATTERY / TEMPERATURE / AUXILIARY ADC |

| TLV320AIC26IRHBR | LOW POWER STEREO AUDIO CODEC WITH HEADPHONE/SPEAKER AMPLIFIER AND 12-BIT BATTERY / TEMPERATURE / AUXILIARY ADC |

| TLV320AIC26IRHB | LOW POWER STEREO AUDIO CODEC WITH HEADPHONE/SPEAKER AMPLIFIER AND 12-BIT BATTERY / TEMPERATURE / AUXILIARY ADC |

| TLV320AIC29_07 | STWREO AUDIO CODEC WITH INTERGRATED HEADPHONE AND SPEAKER AMPLIFIERS |

| TLW-102-06-G-D-01 | 4 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC23 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STereo Audio CODEC, 8- to 96kHz, With Integrated Headphone Amplifier |

| TLV320AIC23_06 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23B_06 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23BGQE | 功能描述:接口—CODEC Lo-Pwr Highly Integrated Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。