- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98251 > TLV2548QDWREP (TEXAS INSTRUMENTS INC) 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV2548QDWREP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | PLASTIC, SOIC-20 |

| 文件頁數(shù): | 40/42頁 |

| 文件大小: | 977K |

| 代理商: | TLV2548QDWREP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁

TLV2544Q, TLV2548Q, TLV2548M

3V TO 5.5V, 12BIT, 200KSPS, 4/8CHANNEL, LOW POWER

SERIAL ANALOGTODIGITAL CONVERTERS WITH AUTOPOWERDOWN

SGLS119F FEBRUARY 2002 REVISED OCTOBER 2009

7

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

control and timing (continued)

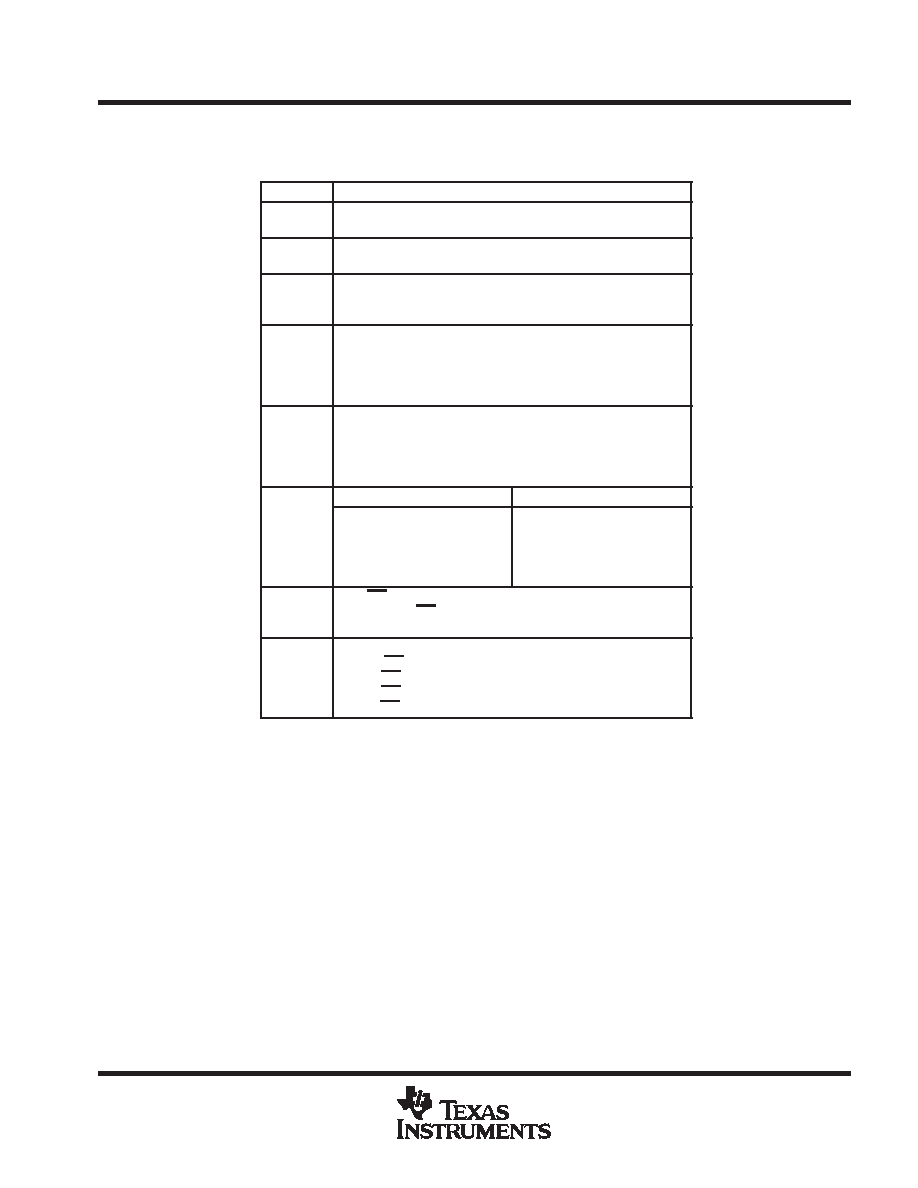

Table 2. TLV2544/TLV2548 Configuration Register (CFR) Bit Definitions

BIT

DEFINITION

D11

Reference select

0: External

1: internal

D10

Internal reference voltage select

0: Internal ref = 4 V 1: internal ref = 2 V

D9

Sample period select

0: Short sampling 12 SCLKs (1x sampling time)

1: Long sampling 24 SCLKs (2x sampling time)

D(87)

Conversion clock source select

00: Conversion clock = internal OSC

01: Conversion clock = SCLK

10: Conversion clock = SCLK/4

11: Conversion clock = SCLK/2

D(6,5)

Conversion mode select

00: Single shot mode [FIFO not used, D(1,0) has no effect.]

01: Repeat mode

10: Sweep mode

11: Repeat sweep mode

D(4,3)

TLV2548

TLV2544

D(4,3)

Sweep auto sequence select

00: 01234567

01: 02460246

10: 00224466

11: 02020202

Sweep auto sequence select

00: N/A

01: 01230123

10: 00112233

11: 01010101

D2

EOC/INT pin function select

0: Pin used as INT

1: Pin used as EOC

D(1,0)

FIFO trigger level (sweep sequence length)

00: Full (INT generated after FIFO level 7 filled)

01: 3/4 (INT generated after FIFO level 5 filled)

10: 1/2 (INT generated after FIFO level 3 filled)

11: 1/4 (INT generated after FIFO level 1 filled)

These bits only take effect in conversion modes 10 and 11.

sampling

The sampling period starts after the first 4 input data are shifted in if they are decoded as one of the conversion

commands. These are select analog input (channel 0 through 7) and select test (channel 1 through 3).

normal sampling

When the converter is using normal sampling, the sampling period is programmable. It can be 12 SCLKs (short

sampling) or 24 SCLKs (long sampling). Long sampling helps when SCLK is faster than 10 MHz or when input

source resistance is high.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV2545IDGKRG4 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2545CDGKRG4 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2545IDRG4 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2548CDWR | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2548CPW | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV2548QDWRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Auto Cat 12B 200 kSPS ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2553EVM | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開發(fā)工具 TLV2553 Eval Mod RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評(píng)估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| TLV2553EVM-PDK | 功能描述:TLV2553 - 12 Bit 200k Samples per Second Analog to Digital Converter (ADC) Evaluation Board 制造商:texas instruments 系列:- 零件狀態(tài):有效 A/D 轉(zhuǎn)換器數(shù):1 位數(shù):12 采樣率(每秒):200k 數(shù)據(jù)接口:SPI 輸入范圍:0 ~ VREF 不同條件下的功率(典型值):- 使用的 IC/零件:TLV2553 所含物品:板 標(biāo)準(zhǔn)包裝:1 |

| TLV2553IDW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2553IDWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。