- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98229 > THS8135PHP (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | THS8135PHP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| 封裝: | GREEN, PLASTIC, HTQFP-48 |

| 文件頁數(shù): | 9/25頁 |

| 文件大小: | 522K |

| 代理商: | THS8135PHP |

THS8135

TRIPLE 10BIT, 240 MSPS VIDEO DAC WITH TRILEVEL SYNC AND VIDEO

(ITUR.BT601)COMPLIANT FULL SCALE RANGE

SLAS343A MAY 2001 REVISED JUNE 2002

17

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

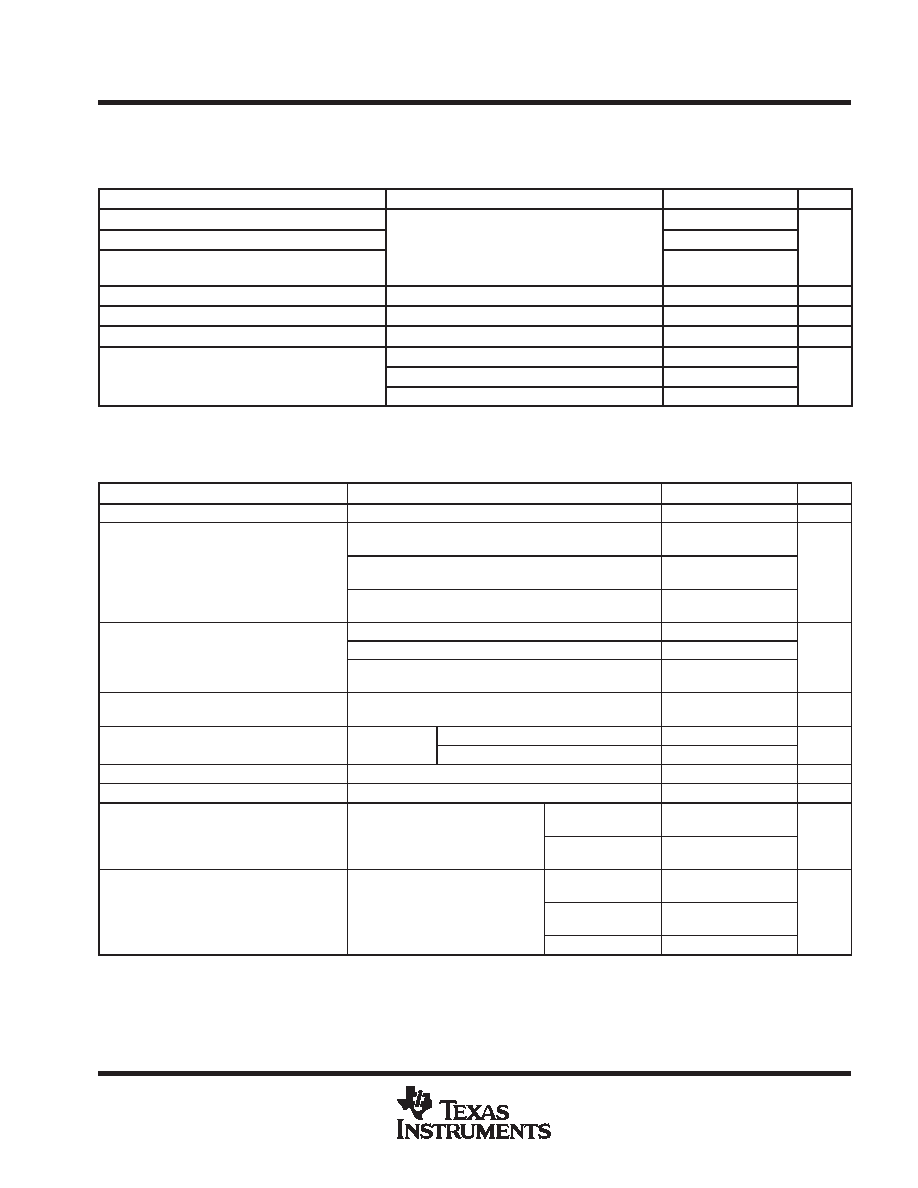

electrical characteristics over recommended operating conditions with fCLK = 240 MSPS and use

of internal reference voltage VREF, with RFS = RFS(nom) (unless otherwise noted) (continued)

digital inputs—dc characteristics

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

IIH

High-level input current

AV

= 3.3 V, DV

= 1.8 V,

1

IIL

Low-level input current

AVDD = 3.3 V, DVDD = 1.8 V,

Digital inputs and CLK at 0 V for IIL;

1

A

IIL(CLK)

Low-level input current, CLK and IIH(CLK)

High-level input current, CLK

Digital inputs and CLK at 0 V for IIL;

Digital inputs and CLK at 2 V for IIH

1

A

CI

Input capacitance

TA = 25_C

5

pF

ts

Data and control inputs setup time

2

ns

th

Data and control inputs hold time

500

ps

Digital process delay from first registered

RGB and YCbCr 4:4:4

7.5

CLK

td(D)

Digital process delay from first registered

color component of pixel

YCbCr 4:2:2 2 x 10 bit

9.5

CLK

periods

td(D)

color component of pixel

YCbCr 4:2:2 1 x 10 bit

10.5

periods

This parameter is assured by design. The digital process delay is defined as the number of CLK cycles required for the first registered color

component of a pixel, starting from the time of registering it on the input bus, to propagate through all processing and appear at the DAC output

drivers. The remaining delay through the IC is the analog delay td(A) of the analog output drivers.

analog (DAC) outputs

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

DAC resolution

10

Bits

Static, best-fit, sync-onall, video mode, RGB full-scale

1.1/

0.9

2/

1.5

INL

Integral nonlinearity

Static, best-fit, sync-on-all, video mode,

RGB ITU.RBT601

1.2/

0.8

2/

1.5

LSB

Static, best fit, generic mode, 1.3 V

1.61/

0.94

2/

1.5

Static, sync-on-all, video mode, RGB full-scale

±0.4

±1

DNL

Differential nonlinearity

Static, sync-on-all, video mode, RGB ITU.RBT601

±0.5

±1

LSB

DNL

Differential nonlinearity

Static, generic mode, 1.3 V

0.32/

0.24

LSB

PSRR

Power supply ripple rejection

ratio of DAC output (full scale)

f = DC, See Note 2

38.5

dB

XTALK

Crosstalk between channels

See Note 3

f = 1 MHz

63

dB

XTALK

Crosstalk between channels

See Note 3

f = 30 MHz

39

dB

Vrefo

Voltage reference output

1.13

1.15

1.16

V

RR

VREF output resistance

276.5

284

294

KIMBAL

Imbalance between DACs

CLK = 80 MSPS, See Note 4

Video mode,

RGB full-scale

2%

1.8%

2%

KIMBAL

Imbalance between DACs

CLK = 80 MSPS, See Note 4

Video mode,

RGB ITU-R.BT601

3%

2.8%

3%

DAC output compliance voltage

Video mode,

RGB full-scale

0.7

VOC

DAC output compliance voltage

(video only)

See Note 5

Video mode, RGB

ITU-R.BT601

0.817

V

Generic mode

1.3

NOTES:

2. PSRR is measured with a 0.1

F capacitor between the COMP and AVDD pin; with a 0.1F capacitor connected between the VREF

pin and AVSS. The ripple amplitude is within the range 100 mVpp to 500 mVpp with the DAC output set to full scale and a

double-terminated 75

(= 37.5 ) load. PSRR is defined as 20 x log(ripple voltage at DAC output/ripple voltage at AVDD input).

Limits from characterization only.

3. Crosstalk spec applies to each possible pair of the three DAC outputs. Limits are from characterization only.

4. The imbalance between DACs applies to all possible pairs of the three DACs.

5. Values at RFS=RFS(nom) ; limits from characterization only.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS8135PHPG4 | PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8136IPHPQ1 | PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8136IPHPR | PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8136PHPR | PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8136IPHPRQ1 | PARALLEL, WORD INPUT LOADING, 0.015 us SETTLING TIME, 10-BIT DAC, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS8135PHP | 制造商:Texas Instruments 功能描述:10BIT DAC 240MSPS TRIPLE SMD |

| THS8135PHPG4 | 功能描述:數(shù)字化視頻/模擬轉(zhuǎn)換器集成電路 Tr 10B 240MSPS Video DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:3 輸出類型:Current 轉(zhuǎn)換速率:180 MSPs 分辨率:10 bit 接口類型:Parallel 電壓參考:Internal or External 積分非線性:- 2.5 LSB, 1.5 LSB 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:HTQFP 封裝:Tray |

| THS8136 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT 180-MSPS GRAPHICS AND VIDEO DAC |

| THS8136IPHP | 功能描述:數(shù)字化視頻/模擬轉(zhuǎn)換器集成電路 Triple 10B 180MSPS Graphics & Video DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:3 輸出類型:Current 轉(zhuǎn)換速率:180 MSPs 分辨率:10 bit 接口類型:Parallel 電壓參考:Internal or External 積分非線性:- 2.5 LSB, 1.5 LSB 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:HTQFP 封裝:Tray |

| THS8136IPHPR | 功能描述:數(shù)字化視頻/模擬轉(zhuǎn)換器集成電路 Triple 10B 180MSPS Graphics & Video DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:3 輸出類型:Current 轉(zhuǎn)換速率:180 MSPs 分辨率:10 bit 接口類型:Parallel 電壓參考:Internal or External 積分非線性:- 2.5 LSB, 1.5 LSB 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:HTQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。