- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98226 > THS4227D (TEXAS INSTRUMENTS INC) 3 CHANNEL, VIDEO PREAMPLIFIER, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | THS4227D |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 音頻/視頻放大 |

| 英文描述: | 3 CHANNEL, VIDEO PREAMPLIFIER, PDSO16 |

| 封裝: | PLASTIC, SOIC-16 |

| 文件頁數(shù): | 14/32頁 |

| 文件大?。?/td> | 411K |

| 代理商: | THS4227D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

THS4221, THS4225

THS4222, THS4226

THS4223, THS4227

SLOS399C – AUGUST 2002 – REVISED JANUARY 2003

www.ti.com

21

P

Dmax +

Tmax–TA

q

JA

where:

PDmax is the maximum power dissipation in the amplifier (W).

Tmax is the absolute maximum junction temperature (°C).

TA is the ambient temperature (°C).

θJA = θJC + θCA

θJC is the thermal coefficient from the silicon junctions to the

case (

°C/W).

θCA is the thermal coefficient from the case to ambient air

(

°C/W).

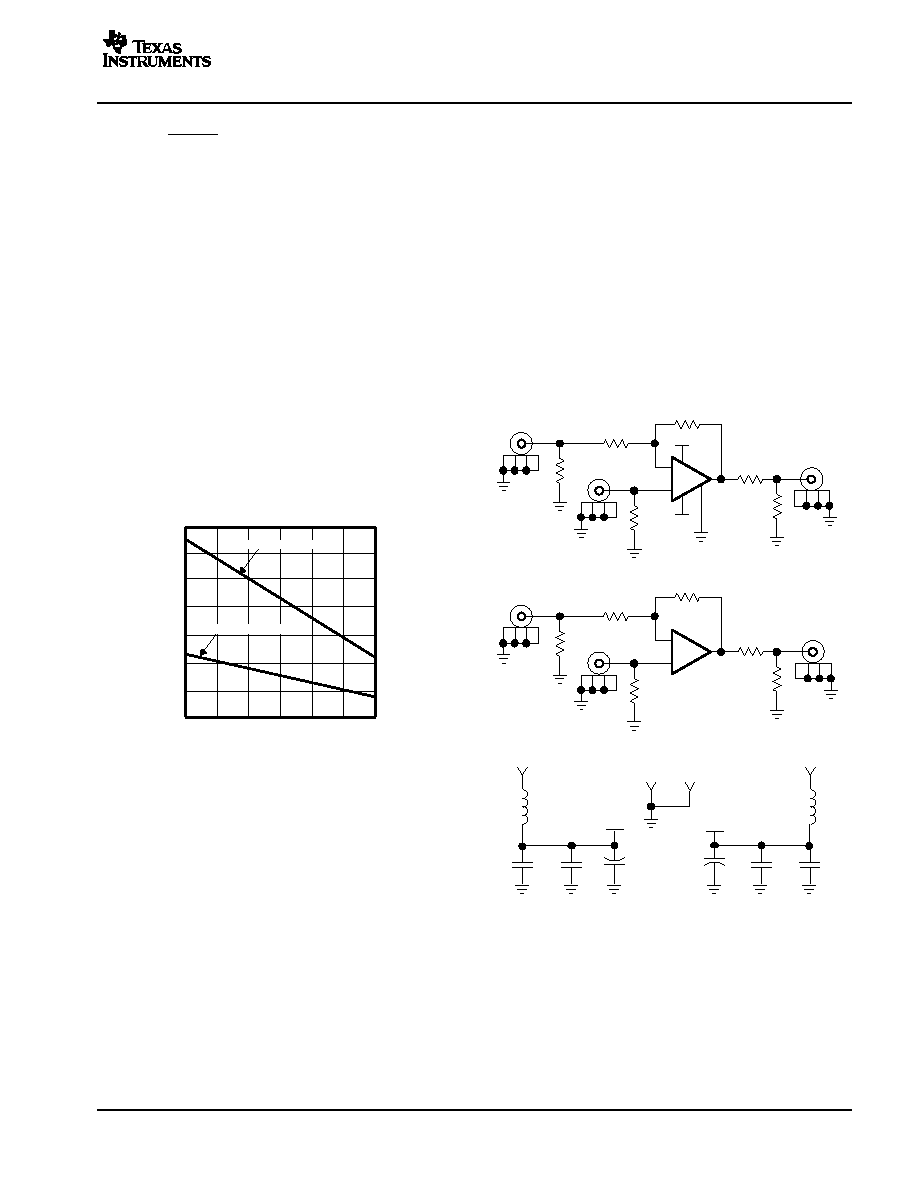

For systems where heat dissipation is more critical, the

THS4222 family is offered in MSOP and TSSOP with

PowerPAD. The thermal coefficient for the MSOP

PowerPAD package is substantially improved over the

traditional SOIC. Maximum power dissipation levels are

depicted in the graph for the two packages. The data for

the DGN package assumes a board layout that follows the

PowerPAD layout guidelines referenced above and

detailed in the PowerPAD application notes in the

Additional Reference Material section at the end of the

data sheet.

2

1.5

1

0

–40

–20

0

20

–

Maximum

Power

Dissipation

–

W

2.5

3

3.5

40

60

80

TA – Ambient Temperature – °C

P

D

8-Pin DGN Package

θJA = 170°C/W for 8-Pin SOIC (D)

θJA = 58.4°C/W for 8-Pin MSOP (DGN)

ΤJ = 150°C, No Airflow

Figure 38. Maximum Power Dissipation vs

Ambient Temperature

0.5

8-Pin D Package

When determining whether or not the device satisfies the

maximum power dissipation requirement, it is important to

consider not only quiescent power dissipation, but also

dynamic power dissipation. Often maximum power

dissipation is difficult to quantify because the signal pattern

is inconsistent, but an estimate of the RMS power

dissipation can provide visibility into a possible problem.

DESIGN TOOLS

Evaluation Fixtures, Spice Models, and

Applications Support

Texas Instruments is committed to providing its customers

with the highest quality of applications support. To support

this goal, evaluation boards have been developed for the

THS4222 family of operational amplifiers. The boards are

easy to use, allowing for straight-forward evaluation of the

device. These evaluation boards can be ordered through

the Texas Instruments web site, www.ti.com, or through

your local Texas Instruments sales representative.

Schematics for the two evaluation boards are shown

below with their default component values. Unpopulated

footprints are shown to provide insight into design

flexibility.

Figure 39. THS4222 EVM Circuit

Configuration

VS+

PwrPad

U1:A

R6

R3

J3

R1

R2

R6

R4

J1

J2

TP1

U1:B

R7

R10

J5

R8

R9

R11

R12

J6

J4

+

C6

VS–

J7

C7

C9

C5

VS+

J9

+

FB2

C10

C8

FB1

VS–

GND

VS+

VS–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS4225DGNRG4 | 1 CHANNEL, VIDEO PREAMPLIFIER, PDSO8 |

| THS4221DGNRG4 | 1 CHANNEL, VIDEO PREAMPLIFIER, PDSO8 |

| THS4226DGQRG4 | 1 CHANNEL, VIDEO PREAMPLIFIER, PDSO10 |

| THS4221DRG4 | 1 CHANNEL, VIDEO PREAMPLIFIER, PDSO8 |

| THS4225DRG4 | 1 CHANNEL, VIDEO PREAMPLIFIER, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS4227PWP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| THS4271 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:LOW NOISE, HIGH SLEW RATE, UNITY GAIN STABLE VOLTAGE FREEBACK AMPLIFIER |

| THS4271D | 功能描述:高速運(yùn)算放大器 Super-Fast Ultra-Low Distortion RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 電壓增益 dB:116 dB 輸入補(bǔ)償電壓:0.5 mV 轉(zhuǎn)換速度:55 V/us 工作電源電壓:36 V 電源電流:7.5 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

| THS4271D | 制造商:Texas Instruments 功能描述:OP AMP HIGH SPEED VFB 4271 SOIC8 |

| THS4271DG4 | 功能描述:高速運(yùn)算放大器 Super-Fast Ultra-Low Distortion RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 電壓增益 dB:116 dB 輸入補(bǔ)償電壓:0.5 mV 轉(zhuǎn)換速度:55 V/us 工作電源電壓:36 V 電源電流:7.5 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。