THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

16

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

FIFO description

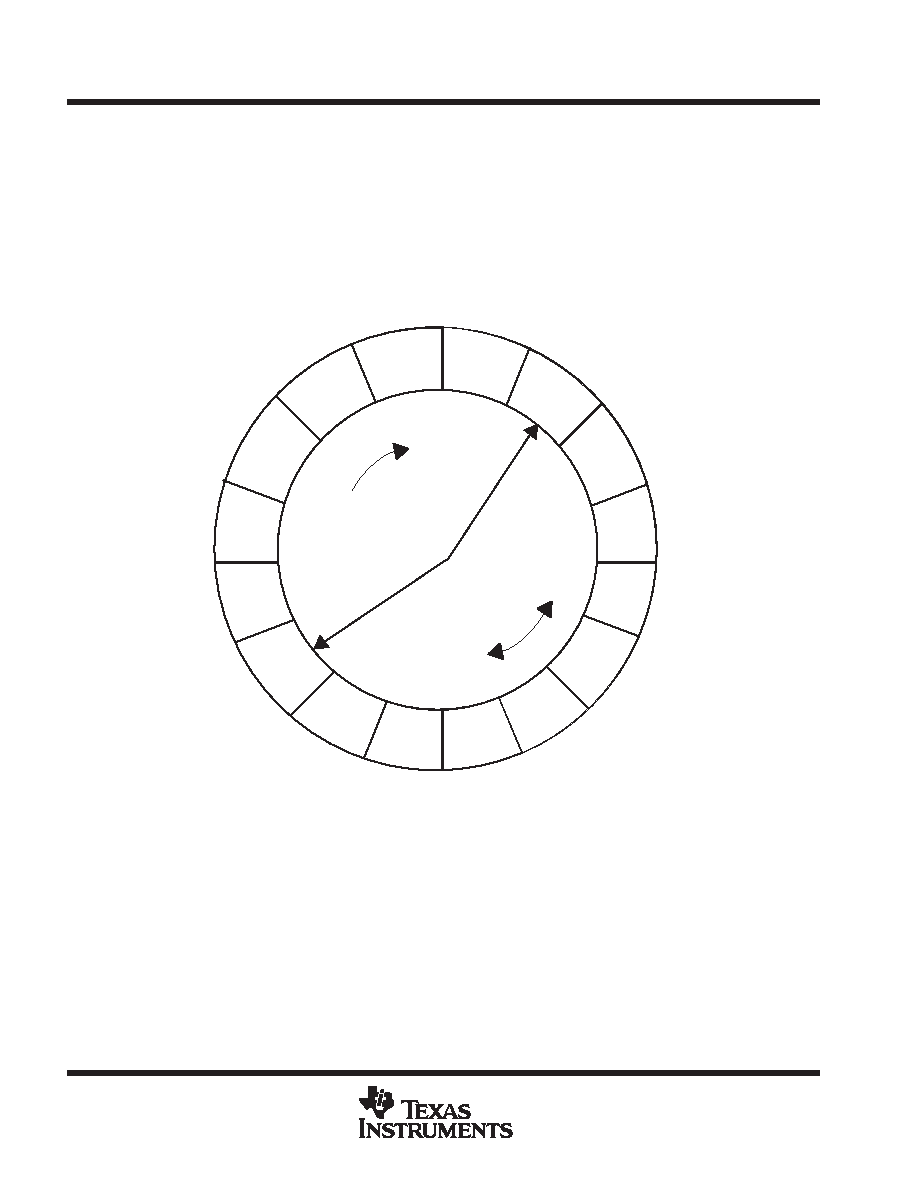

The FIFO is based on a circular buffer (see Figure 15, in this example the FIFO is 16 words long). The buffer is

accessed using two pointers, one for the ADC writing to the FIFO, one for the processor (DSP) reading from the buffer.

Both pointers move in a clockwise direction. If the distance between the ADC write pointer and the DSP read pointer

is greater or equal a programmable threshold, the INT signal is asserted. If this INT signal is connected to an external

interrupt pin of the processor, it is possible to read out the stored values in the FIFO at once during the interrupt service

routine. If the ADC write pointer reaches the position of the DSP read pointer, an overflow occurs. In this case, the

overflow bit in the ADC register is set and the FOVL is asserted.

7

8

9

10

11

12

13

14

15

0

1

2

3

4

5

6

ADC

DSP

T

Figure 15. Circular Buffer