- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371180 > T8533 T8533/34 Quad Programmable Line Card Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | T8533 |

| 英文描述: | T8533/34 Quad Programmable Line Card Signal Processor |

| 中文描述: | T8533/34四線卡可編程信號(hào)處理器 |

| 文件頁(yè)數(shù): | 38/48頁(yè) |

| 文件大小: | 890K |

| 代理商: | T8533 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

Preliminary Data Sheet

July 2001

Signal Processor

T8533/34 Quad Programmable Line Card

38

Agere Systems Inc.

Software Interface

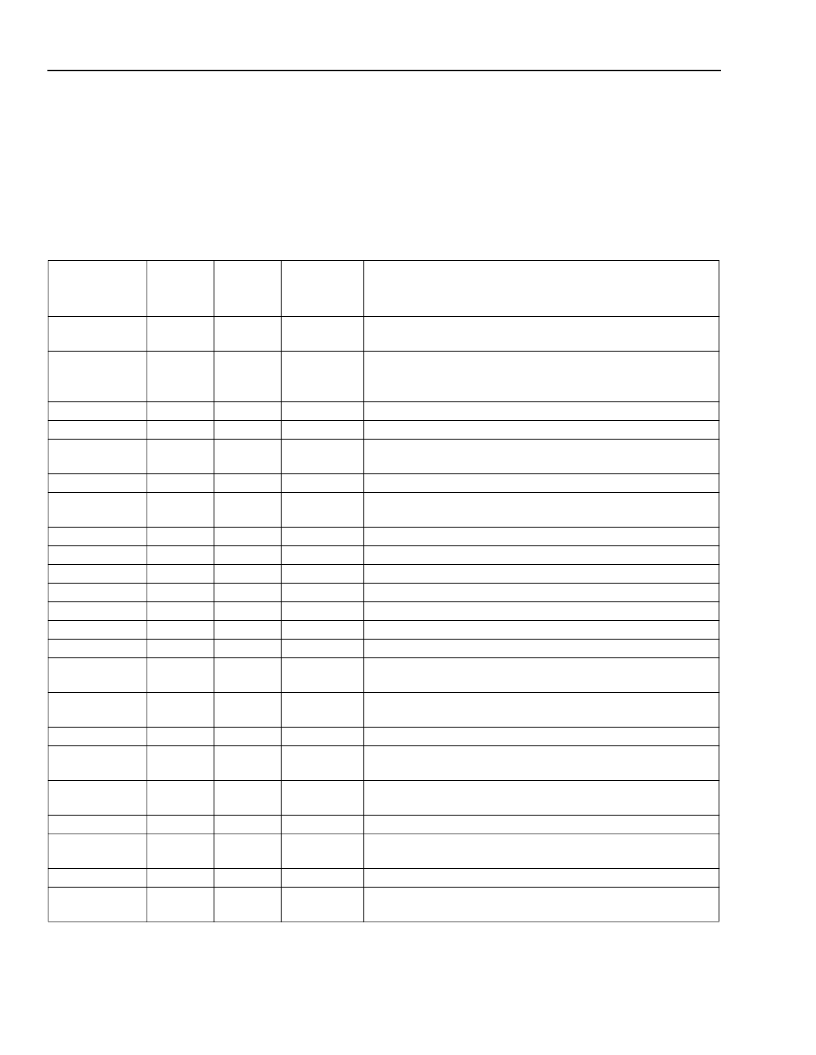

Table 17. Memory Mapping

With the exceptions noted, all of these memory locations may be read to determine the state of the controls con-

tained therein. In the following table, bit 0 is the LSB (transmitted first on the serial interface) and bit 7 is the most

significant bit of the byte. Unused bits in an address or multibyte address should be loaded as zero. All of the mem-

ory locations can be programmed on a per-channel basis.

Note that the entire coefficient set for a channel (or all four channels) may be loaded with one command.

* The coefficients to be entered can be obtained from the Aquarium coefficient software.

Control Name

Address

(decimal)

Number

of Bits

Used

1024

Default

Value

Name/Description

HBALTAPS*

0—127

See Table

18

0x00

Balance impedance tap coefficients.

RESCTRL

128

4

Reset address. Writing a 1 in the used positions causes a

reset as defined by the bit definition. This reset remains in

force until the bit is written as a 0.

Standby/active control.

Bit offset for receive direction.

Time-slot offset for receive direction.

CHACTIVE

RXBITOFF

RXOFF

129

130

131

1

3

8

0x00

0x00

(16*

channel #)

0x0400

0x01ac

GRX1*

GRX2*

132—133

134—135

11

11

Control of gain affecting receive direction gain transfer.

Control of gain sensitive to impedance and SLIC parameter

choices, receive direction.

Peak and far-end speech detector control.

Near-end speech detector control.

Adaptation control address.

Data call control address.

0x07ed0000 CTZ bleed coefficients.

0x01

Adaptation leak values.

0x00

Residual echo control.

0x19

RTZ, transmit analog gain (XAG), and analog loopback

controls.

(17*

channel #)

state referenced in this data sheet.

0x0400

Control of gain affecting transmit direction gain transfer.

0x000000

Coefficients for the equalization stage that accommodates

current-sensing SLICs.

0x051a

Control of gain sensitive to impedance and SLIC parameter

choices, transmit direction.

0x00

Bit offset for transmit direction.

(16*

channel #)

0x00

PCM control address.

0x0c

SLIC 3-state control address. A 1 enables the correspond-

ing SLIC pin to operate as an output pin.

NORMCTRL*

NESCTRL*

LMSGAIN*

TDETCTRL*

CTZCTRL*

LMSCTRL*

RECCTRL*

SDCTRL*

136

137

138

139

6

3

8

6

31

3

5

7

0x25

0x06

0xee

0x00

140—143

144

145

146

SDTSI

147

7

Internal time-slot interchanger. Default sets external pins to

GTX2*

ZEQCTRL*

148—149

150—152

12

21

GTX1*

153—154

12

TXBITOFF

TXOFF

155

156

3

8

Time-slot offset for transmit direction.

PCMCTRL

SLICTS

157

158

7

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8534 | T8533/34 Quad Programmable Line Card Signal Processor |

| T8535B | T8535B/T8536B Quad Programmable Codec |

| T8536B | T8535B/T8536B Quad Programmable Codec |

| T8538B | T8538B Quad Programmable Codec |

| T923CFAA | T92-Type 10 Gbits/s 1300 nm Uncooled DFB Laser Transmitter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T85331G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85331J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T8534 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8533/34 Quad Programmable Line Card Signal Processor |

| T8535B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

| T8536B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。