- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361357 > T81L0003B-BK (TM Technology, Inc.) 8-bit MCU PDF資料下載

參數(shù)資料

| 型號: | T81L0003B-BK |

| 廠商: | TM Technology, Inc. |

| 英文描述: | 8-bit MCU |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 11/16頁 |

| 文件大小: | 100K |

| 代理商: | T81L0003B-BK |

TE

CH

tm

T81L0003B

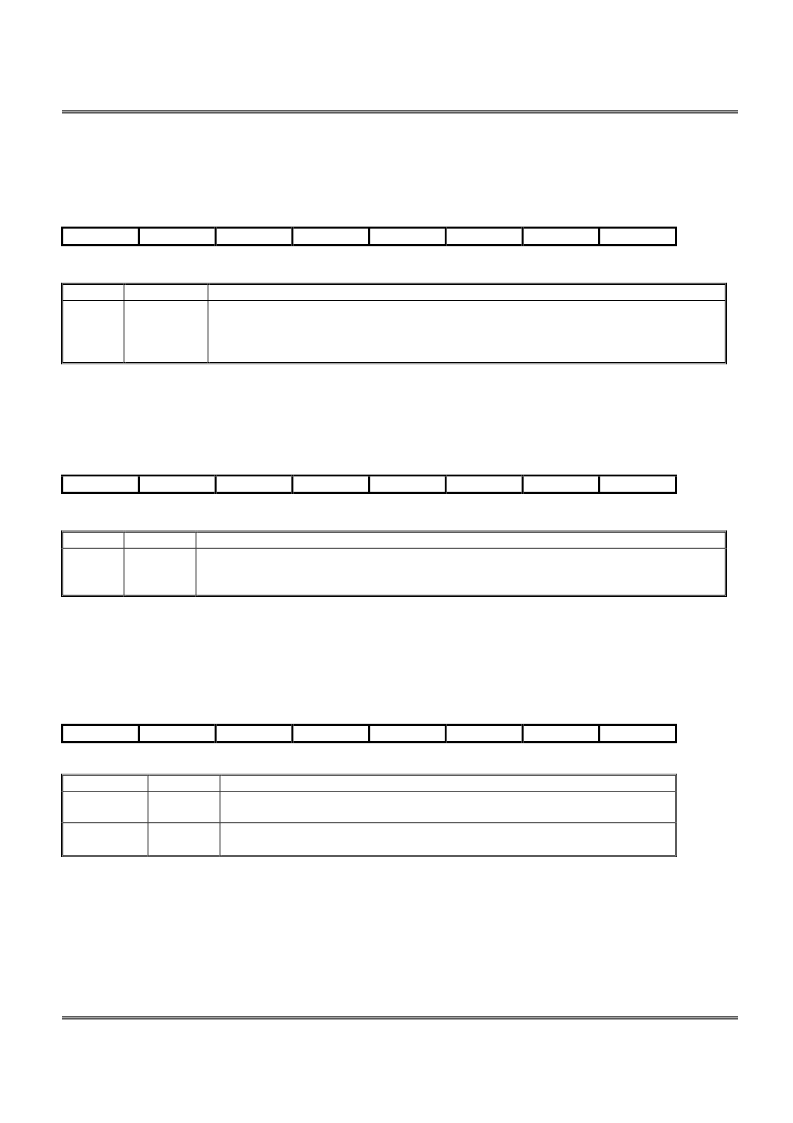

Special Function Registers

a) Interrupt Enable 0 register (ien0)

The ien0 register (address : A8)

MSB

eal

The ien0 bit functions

Bit

Symbol

TM Technology Inc. reserves the right

P. 11

Publication Date: NOV. 2005

to change products or specifications without notice. Revision:A

LSB

ex0

wdt

et2

es0

et1

ex1

et0

Function

Watchdog timer refresh flag.

Set to initiate a refresh of the watchdog timer. Must be set directly before swdt is set to prevent

an unintentional refresh of the watchdog timer. The wdt is reset by hardware 12 instruction

cycles after it has been set.

Note: other bits are not used to watchdog control

The ien0 bit functions

b) Interrupt Enable 1 register (ien1)

The ien1 register (Address : B8)

MSB

-

swdt

pt2

ps

The ien1 bit functions

Bit

Symbol

Function

Watchdog timer start refresh flag.

Set to active/refresh the watchdog timer. When directly set after setting wdt, a watchdog timer

refresh is performed. Bit swdt is reset by hardware 12 instruction cycles after it has been set.

Pay attention that when write ien1.6, it write the swdt bit, when read ien1.6, we will read out the wdts bit. Ie. Watch dog

timer status flag. Set by hardware when the watchdog timer was started.

c) Watchdog Timer Reload register (wdtrel)

The wdtrel register ( Address : 86 )

MSB

7

6

5

4

The wdtrel bit functions

Bit

Symbol

Function

Prescaler select bit. When set, the watchdog is clocked through an additional

divide-by-16 prescaler

wdtrel.6 t0

wdtrel.0

to the wdt when a refresh is triggered by a consecutive setting of bits wdt and swdt

The wdtrel register can be loaded and read any time

ien0.6

wdt

LSB

px0

pt1

px1

pt0

Ien1.6

swdt

LSB

0

3

2

1

wdtrel.7

7

6-0

Seven bit reload value for the high-byte of the watchdog timer. This value is loaded

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T81L0006A | 8-bit A/D Type MCU |

| T81L0006A-AD | 8-bit A/D Type MCU |

| T81L0006B-AD | 8-bit A/D Type MCU |

| T81L0006B-AK | 8-bit A/D Type MCU |

| T81L0006B-BD | 8-bit A/D Type MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T81L0006A | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit A/D Type MCU |

| T81L0006A_06 | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit A/D Type MCU |

| T81L0006A-AD | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit A/D Type MCU |

| T81L0006A-AK | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit A/D Type MCU |

| T81L0006A-BD | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit A/D Type MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。