- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98144 > ST6382B1/XXX (STMICROELECTRONICS) 8-BIT, MROM, MICROCONTROLLER, PDIP42 PDF資料下載

參數(shù)資料

| 型號: | ST6382B1/XXX |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, MICROCONTROLLER, PDIP42 |

| 封裝: | PLASTIC, SDIP-42 |

| 文件頁數(shù): | 37/82頁 |

| 文件大小: | 1651K |

| 代理商: | ST6382B1/XXX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

Obsolete

Product(s)

- Obsolete

Product(s)

42/82

ST6388, ST63E88, ST63T88

SERIAL PERIPHERAL INTERFACE (Cont’d)

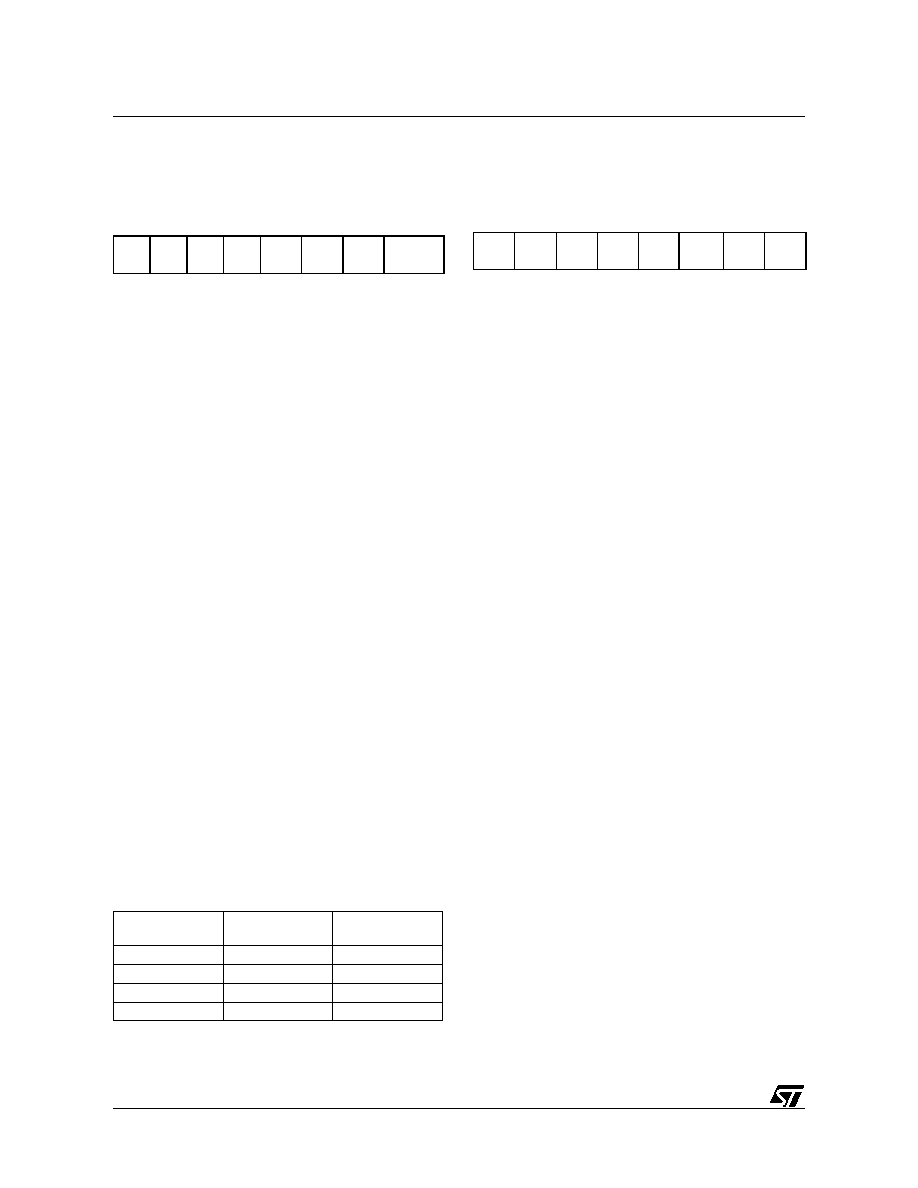

SPI Control Register 1 (SCR1)

Address: EBh - Write only

Reset Value: 00h

Caution: This register contains at least one write

only bit. Single bit instructions (SET, RES, INC

and DEC) should not be used.

b7-b4. These bits are not used.

STR. This is Start bit for I2C BUS/S-BUS. This bit

is meaningless when STD/SPI enable bit is

cleared to zero. If this bit is set to one and STD/SPI

bit is also set to “1” then SPI Start generation, be-

fore beginning of transmission, is enabled. Set to

zero after reset.

STP. This is Stop bit for I2C BUS/S-BUS. This bit

is meaningless when STD/SPI enable bit is

cleared to zero. If this bit is set to one and STD/SPI

bit is also set to “1” then SPI Stop condition gener-

ation is enabled. STP bit must be reset when

standard protocol is used (this is also the default

reset conditions). Set to zero after reset.

STD, SPI Enable. This bit, in conjunction with S-

BUS/I2C BUS bit, allows the SPI disable and will

select between I2C BUS/S-BUS and Standard

shift register protocols. If this bit is set to one, it se-

lects both I2C BUS and S-BUS protocols; final se-

lection between them is made by S-BUS/I2C BUS

bit. If this bit is cleared to zero when S-BUS/I2C

BUS is set to “1” the Standard shift register proto-

col is selected. If this bit is cleared to “0” when S-

BUS/I2C BUS is cleared to 0 the SPI is disabled.

Set to zero after reset.

S-BUS/I2C BUS Selection. This bit, in conjunction

with STD/SPI bit, allows the SPI disable and will

select between I2C BUS and S-BUS protocols. If

this bit is cleared to “0” when STD bit is also “0”,

the SPI interface is disabled. If this bit is cleared to

zero when STD bit is set to “1”, the I2C BUS proto-

col will be selected. If this bit is set to “1” when

STD bit is set to “1”, the S-BUS protocol will be se-

lected. Cleared to zero after reset.

Table 13. SPI Mode Selection

SPI Control Register 2 (SCR2)

Address: ECh - Read/Write

Reset Value: 00h

Caution: This register contains at least one write

only bit. Single bit instructions (SET, RES, INC

and DEC) should not be used.

b7-b4. These bits are not used.

TX/RX. Write Only. When this bit is set, current

byte operation is a transmission. When it is reset,

current operation is a reception. Set to zero after

reset.

VRY/S. Read Only/Write Only. This bit has two dif-

ferent functions in relation to read or write opera-

tion. Reading Operation: when STD and/or TRX

bits is cleared to 0, this bit is meaningless. When

bits STD and TX are set to 1, this bit is set each

time BSY bit is set. This bit is reset during byte op-

eration if real data on SDA line are different from

the output from the shift register. Set to zero after

reset. Writing Operation: it enables (if set to one)

or disables (if cleared to zero) the interrupt coming

from VSYNC pin. Undefined after reset. Refer to

OSD description for additional information.

ACN. Read Only. If STD bit (D1 of SCR1 register)

is cleared to zero this bit is meaningless. When

STD is set to one, this bit is set to one if no Ac-

knowledge has been received. In this case it is au-

tomatically reset when BSY is set again. Set to

zero after reset.

BSY. Read/Set Only. This is the busy bit. When a

one is loaded into this bit the SPI interface start the

transmission of the data byte loaded into SSDR

data register or receiving and building the receive

data into the SSDR data register. This is done in

accordance with the protocol, direction and start/

stop condition(s). This bit is automatically cleared

at the end of the current byte operation. Cleared to

zero after reset.

Note: The SPI shift register is also the data trans-

mission register and the data received register;

this feature is made possible by using the serial

structure of the ST638x and thus reducing size

and complexity.

70

--

STR

STP

STD/

SPI

S-BUS/

I

2

CBUS

D1

STD/SP

D0

S-BUS/I

2C BUS

SPI Function

0

Disabled

0

1

STD Shift Reg.

10

I2C BUS

1

S-BUS

70

-

TX/RX VRY/S

ACN

BSY

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST6386B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6388B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6387B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6394B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6399B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST6382B4 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST6383 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST6383B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST6383B4 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST6385 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。