- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376418 > SPAKMC332VFV20 (MOTOROLA INC) 32-Bit Modular Microcontroller PDF資料下載

參數(shù)資料

| 型號: | SPAKMC332VFV20 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-Bit Modular Microcontroller |

| 中文描述: | 32-BIT, 20 MHz, MICROCONTROLLER, PQFP144 |

| 封裝: | QFP-144 |

| 文件頁數(shù): | 25/88頁 |

| 文件大?。?/td> | 446K |

| 代理商: | SPAKMC332VFV20 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

MC68332

MC68332TS/D

MOTOROLA

25

3.3.3 Clock Control

The clock control circuits determine system clock frequency and clock operation under special circum-

stances, such as following loss of synthesizer reference or during low-power operation. Clock source is

determined by the logic state of the MODCLK pin during reset.

When the on-chip clock synthesizer is used, system clock frequency is controlled by the bits in the upper

byte of SYNCR. Bits in the lower byte show status of or control operation of internal and external clocks.

The SYNCR can be read or written only when the CPU is operating at the supervisor privilege level.

W — Frequency Control (VCO)

This bit controls a prescaler tap in the synthesizer feedback loop. Setting the bit increases the VCO

speed by a factor of four. VCO relock delay is required.

X — Frequency Control Bit (Prescale)

This bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting the bit

doubles clock speed without changing the VCO speed. There is no VCO relock delay.

Y[5:0] — Frequency Control (Counter)

The Y field controls the modulus down counter in the synthesizer feedback loop, causing it to divide by

a value of Y

+

1. Values range from 0 to 63. VCO relock delay is required.

EDIV — E Clock Divide Rate

0 = ECLK frequency is system clock divided by 8.

1 = ECLK frequency is system clock divided by 16.

ECLK is an external M6800 bus clock available on pin ADDR23. Refer to

3.5 Chip Selects

for more

information.

SLIMP — Limp Mode Flag

0 = External crystal is VCO reference.

1 = Loss of crystal reference.

When the on-chip synthesizer is used, loss of reference frequency causes SLIMP to be set. The VCO

continues to run using the base control voltage. Maximum limp frequency is maximum specified system

clock frequency. X-bit state affects limp frequency.

SLOCK — Synthesizer Lock Flag

0 = VCO is enabled, but has not locked.

1 = VCO has locked on the desired frequency (or system clock is external).

The MCU maintains reset state until the synthesizer locks, but SLOCK does not indicate synthesizer

lock status until after the user writes to SYNCR.

RSTEN — Reset Enable

0 = Loss of crystal causes the MCU to operate in limp mode.

1 = Loss of crystal causes system reset.

STSIM — Stop Mode SIM Clock

0 = When LPSTOP is executed, the SIM clock is driven from the crystal oscillator and the VCO is

turned off to conserve power.

1 = When LPSTOP is executed, the SIM clock is driven from the VCO.

STEXT — Stop Mode External Clock

0 = When LPSTOP is executed, the CLKOUT signal is held negated to conserve power.

1 = When LPSTOP is executed, the CLKOUT signal is driven from the SIM clock, as determined by

the state of the STSIM bit.

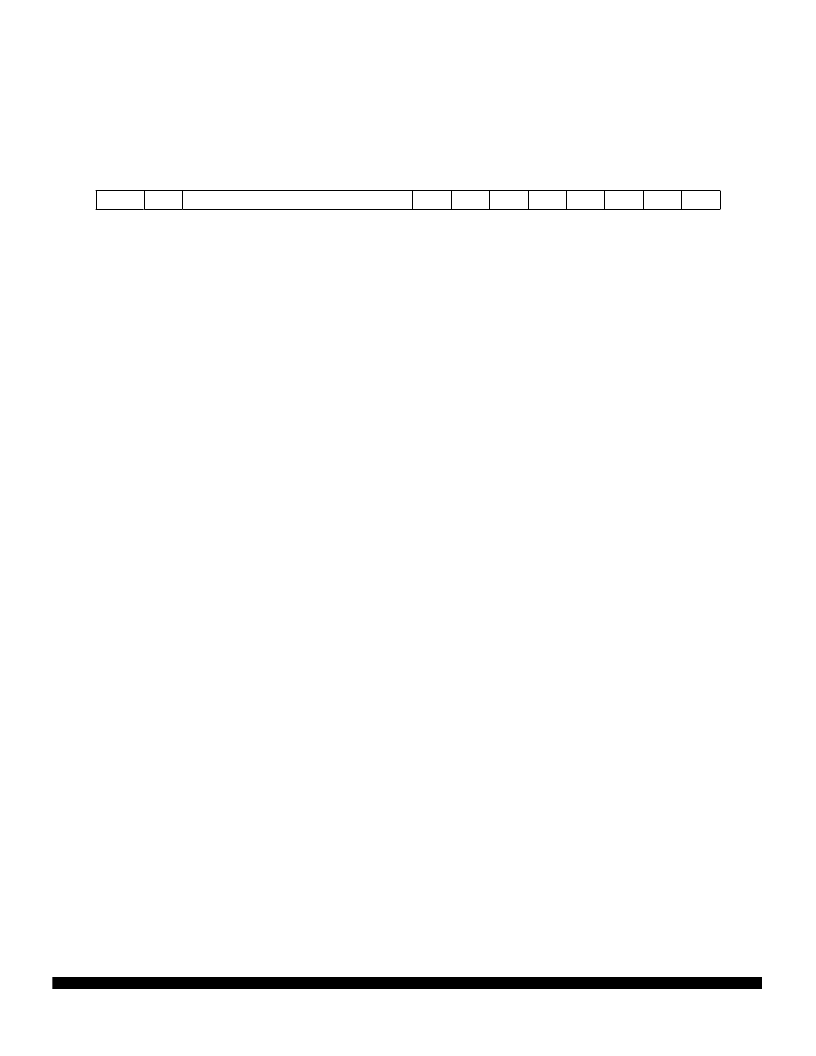

SYNCR

—Clock Synthesizer Control Register

$YFFA04

15

14

13

8

7

6

5

4

3

2

1

0

W

X

Y

EDIV

0

0

SLIMP

SLOCK RSTEN

STSIM

STEXT

RESET:

0

0

1

1

1

1

1

1

0

0

0

U

U

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SPAKMC332AVFV16 | 32-Bit Modular Microcontroller |

| SPAKMC332CFC16 | 32-Bit Modular Microcontroller |

| SPAKMC332CFC20 | 32-Bit Modular Microcontroller |

| SPAKMC332CFV16 | 32-Bit Modular Microcontroller |

| SPAKMC332CFVV20 | 32-Bit Modular Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SPAKVZ328CPV | 制造商:ON SEM 功能描述: |

| SPAKXC301GC100D | 制造商:Motorola Inc 功能描述: |

| SPAKXC301PW100D | 制造商:Motorola Inc 功能描述: |

| SPAKXC309AG100A | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 24 BIT DSP PBFREE RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| SPAKXC309GC100A | 制造商:Motorola 功能描述:MOTOROLA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。