- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1969 > SP510CM-L (Exar Corporation)IC TXRX MULTIPROTOCOL HS 100LQFP PDF資料下載

參數(shù)資料

| 型號: | SP510CM-L |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 28/37頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC TXRX MULTIPROTOCOL HS 100LQFP |

| 特色產(chǎn)品: | SP510 Ultra High Speed 52Mbps 8-Channel Multi-Protocol Transceiver |

| 標準包裝: | 90 |

| 類型: | 收發(fā)器 |

| 驅(qū)動器/接收器數(shù): | 8/8 |

| 規(guī)程: | 多協(xié)議 |

| 電源電壓: | 5V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LQFP |

| 供應(yīng)商設(shè)備封裝: | 100-LQFP(14x14) |

| 包裝: | 托盤 |

| 其它名稱: | 1016-1194 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

SP510

34

ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

REV. 1.0.1

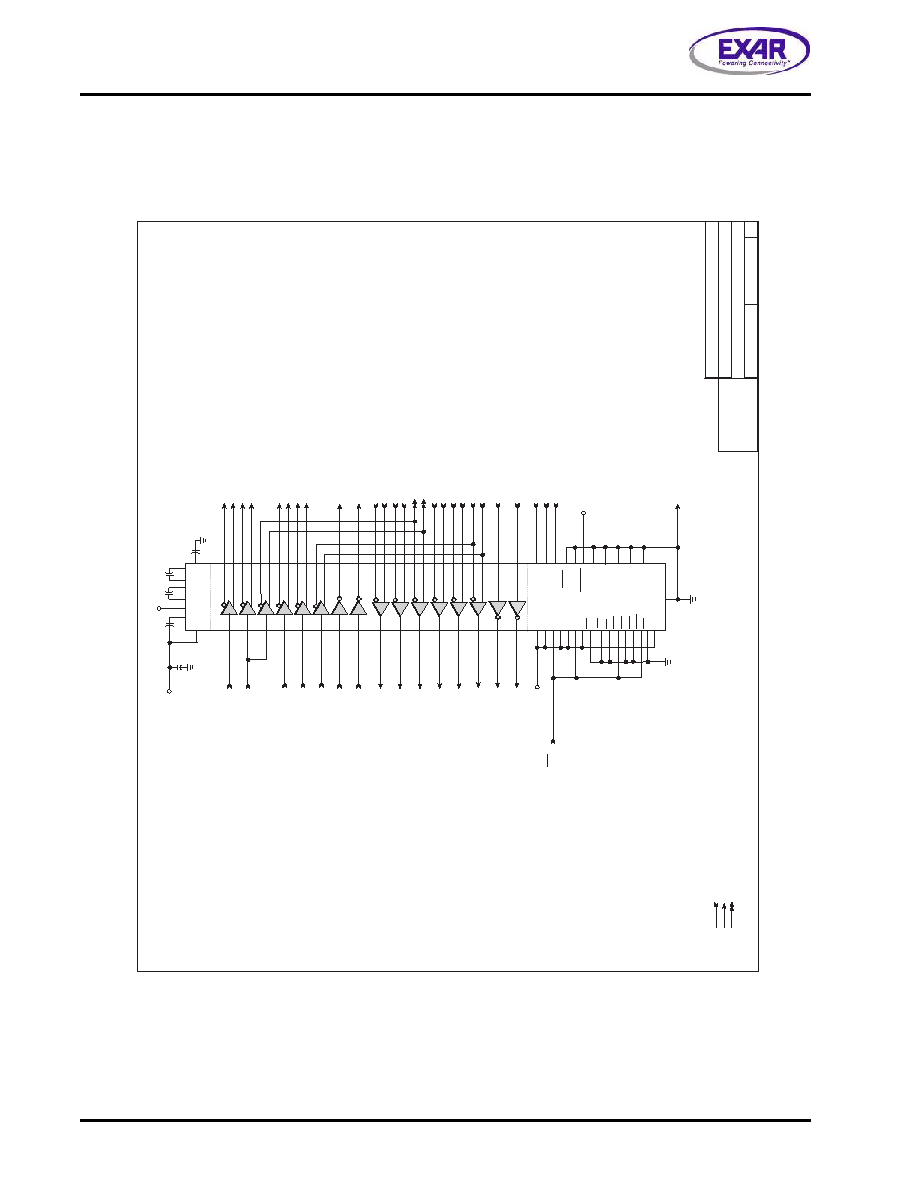

FIGURE 47. TYPICAL OPERATING CONFIGURATION TO SERIAL PORT CONNECTOR WITH DCE/DTE PROGRAMMABIL-

ITY

20

(V

.11,

V.28)

DTR_DSR_A

23

(V

.11)

DTR_DSR_B

1μ

F

1μ

F

1μ

F

V CC

V DD

C1-

C2-

V SS

C1+

C2+

1μ

F

SP510

TxD

TxCE

ST

RT

S

DTR

DCD_DCE

RL

RxC

TxC

CTS

DSR

DCD_DTE

RI

TM

10μ

F

μDB-26

Serial

Port

Connector

Pins

Signal

(DTE_DCE)

2(V

.11,

V.35,

V.28)

TXD_RXD_A

14

(V

.11,

V.35)

TXD_RXD_B

11

(V

.11,

V.35)

TXCE_TXC_B

25

(V

.10,

V.28)

LL_TM

15

(V

.11,

V.35,

V.28)

*TXC_RXC_A

12

(V

.11,

V.35)

*TXC_RXC_B

SDEN

24

(V

.11,

V.35,

V.28)

TXCE_TXC_A

3(V

.11,

V.35,

V.28)

RXD_TXD_A

16

(V

.11,

V.35)

RXD_TXD_B

8(V

.11,

V.28)

DCD_DCD_A

10

(V

.11)

DCD_DCD_B

Typical

SP510

DB-26

Ser

ial

Por

tConfiguration

Customer

:

Title

:

Date

:

Doc.

#

:

Re

v.

0

Refer

ence

Design

Schematic

SIGNAL

GND

(10

Pins)

9(V

.11,

V.35)

RXC_TXCE_B

17

(V

.11,

V.35,

V.28)

RXC_TXCE_A

LLEN

STEN

GND

*-

Dr

iver

applies

f

or

DCE

only

on

pins

15

and

12.

Receiv

er

applies

for

DTE

only

on

pins

15

and

12.

+5V

#103

(TxD)

#108

(DTR)

#105

(R

TS)

#141

(LL)

#105

(RXD)

#115

(RXC)

#106

(CTS)

#107

(DSR)

#109

(DCD)

DTE

I/O

Lines

represented

bydoub

learrowhead

signifies

abi-directional

bus

.

Input

Line

Output

Line

#114

(TxC)

#113

(TXCE)

#109

(DCD)

DCE

LL

RxD

TTEN

TREN

RSEN

RRCEN RLEN

RDEN

TMEN

TxCEN

RTEN

DMEN

CSEN

RR

TEN

ICEN

V10_GND

V35TGND1

V35TGND2

V35TGND3

V35RGND

TERM_OFF

D_LA

TCH

D0

D1

D2

Charge

Pump

Section

Transceiv

erSection

Logic

Section

VL

21

(V

.10,

V.28)

RL_RI

22

(V

.10,

V.28)

RI_RL

18

(V

.10,

V.28)

LL_TM

#125

(RI)

#142

(TM)

#140

(RL)

DCE/DTE

Dr

iver

applies

f

or

DCE

only

on

pins

8

and

10.

Receiv

er

applies

for

DTE

only

on

pins

8

and

10.

LOOPBA

CK

VL

19

(V

.11)

RTS_CTS_B

4(V

.11,

V.28)

RTS_CTS_A

6(V

.11,

V.28)

DSR_DTR_A

22

(V

.11)

DSR_DTR_B

13

(V

.11)

CTS_R

TS_B

5(V

.11,

V.28)

CTS_R

TS_A

VL

Logic

Voltage

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SP526CF-L | IC TXRX WAN MULTI-MODE 44LQFP |

| SP5301CY-L/TR | IC TXRX SERIAL BUS UNIV 14TSSOP |

| SPC5200CBV400 | IC MPU 32BIT 400MHZ 272-PBGA |

| SPC5200CVR400 | IC MPU 32BIT 400MHZ 272-PBGA |

| SPC5517GAMMG66 | IC MCU 32B 1.5MB FLASH 208MAPBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SP510E | 制造商:Ferraz Shawmut 功能描述: |

| SP510ECF-L | 功能描述:RS-232接口集成電路 Ultra High Speed Multiprotocol Xcvr RoHS:否 制造商:Exar 數(shù)據(jù)速率:52 Mbps 工作電源電壓:5 V 電源電流:300 mA 工作溫度范圍:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體:LQFP-100 封裝: |

| SP510EEF-0A-EB | 制造商:Exar Corporation 功能描述:SP510EEF-0A-EB |

| SP510EEF-L | 功能描述:RS-232接口集成電路 Ultra High Speed Multiprotocol Xcvr RoHS:否 制造商:Exar 數(shù)據(jù)速率:52 Mbps 工作電源電壓:5 V 電源電流:300 mA 工作溫度范圍:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體:LQFP-100 封裝: |

| SP510EM | 制造商:EXAR 制造商全稱:EXAR 功能描述:ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復。