- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98127 > SN74LVTH16835DLG4 (TEXAS INSTRUMENTS INC) LVT SERIES, 18-BIT DRIVER, TRUE OUTPUT, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | SN74LVTH16835DLG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | LVT SERIES, 18-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 封裝: | GREEN, PLASTIC, SSOP-56 |

| 文件頁數(shù): | 10/13頁 |

| 文件大小: | 359K |

| 代理商: | SN74LVTH16835DLG4 |

SN54LVTH16835, SN74LVTH16835

3.3-V ABT 18-BIT UNIVERSAL BUS DRIVERS

WITH 3-STATE OUTPUTS

SCBS713C – MARCH 1998 – REVISED APRIL 1999

6

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

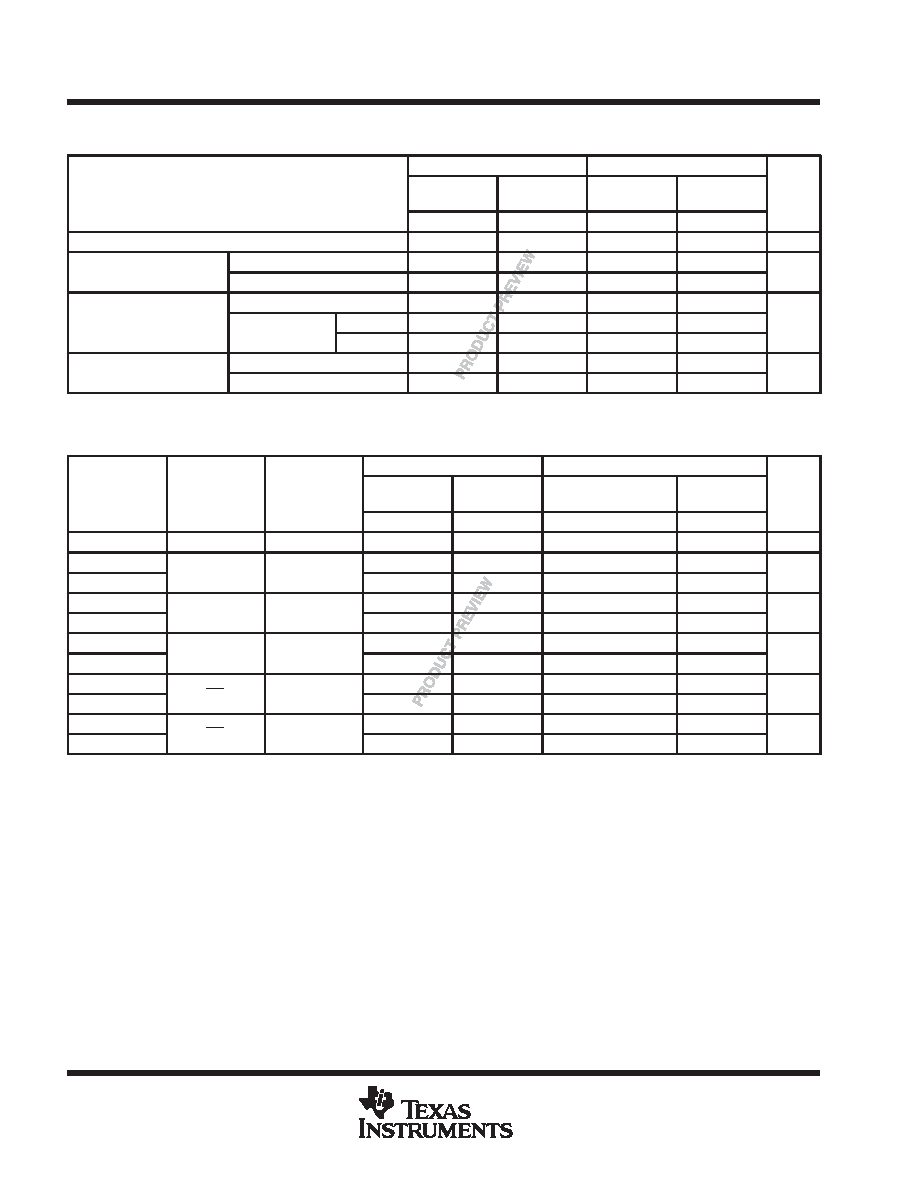

timing requirements over recommended operating free-air temperature range (unless otherwise

noted) (see Figure 1)

SN54LVTH16835

SN74LVTH16835

VCC = 3.3 V

± 0.3 V

VCC = 2.7 V

VCC = 3.3 V

± 0.3 V

VCC = 2.7 V

UNIT

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

fclock

Clock frequency

150

MHz

t

Pulse duration

LE high

3.3

ns

tw

Pulse duration

CLK high or low

3.3

ns

Data before CLK

↑

2.2

2.5

2.1

2.4

tsu

Setup time

Data before LE

↓

CLK high

2.5

1.7

2.3

1.5

ns

Data before LE

↓

CLK low

1.5

0.5

1.5

0.5

th

Hold time

Data after CLK

↑

1

0

1

0

ns

th

Hold time

Data after LE

↓

0.8

ns

switching characteristics over recommended operating free-air temperature range, CL = 50 pF

(unless otherwise noted) (see Figure 1)

SN54LVTH16835

SN74LVTH16835

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

VCC = 3.3 V

± 0.3 V

VCC = 2.7 V

VCC = 3.3 V

± 0.3 V

VCC = 2.7 V

UNIT

MIN

MAX

MIN

MAX

MIN

TYP

MAX

MIN

MAX

fmax

150

MHz

tPLH

A

Y

1.2

3.9

4.3

1.3

2.6

3.7

4

ns

tPHL

A

Y

1.2

3.9

4.3

1.3

2.4

3.7

4

ns

tPLH

LE

Y

1.4

5.3

5.9

1.5

3.2

5.1

5.7

ns

tPHL

LE

Y

1.4

5.3

5.9

1.5

3.3

5.1

5.7

ns

tPLH

CLK

Y

1.4

5.3

5.9

1.5

3.5

5.1

5.7

ns

tPHL

CLK

Y

1.4

5.3

5.9

1.5

3.4

5.1

5.7

ns

tPZH

OE

Y

1.2

5

5.9

1.3

2.9

4.6

5.5

ns

tPZL

OE

Y

1.2

5

5.9

1.3

3

4.6

5.5

ns

tPHZ

OE

Y

1.6

6

6.5

1.7

4.2

5.8

6.3

ns

tPLZ

OE

Y

1.6

6

6.5

1.7

3.7

5.8

6.3

ns

All typical values are at VCC = 3.3 V, TA = 25°C.

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74LVTH16952DLR | LVT SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| SN74LVTH182514DGG | LVT SERIES, 20-BIT BOUNDARY SCAN REG TRANSCEIVER, TRUE OUTPUT, PDSO64 |

| SN74LVTH18514DGG | LVT SERIES, 20-BIT BOUNDARY SCAN REG TRANSCEIVER, TRUE OUTPUT, PDSO64 |

| SN74LVTH18640DL | LVT SERIES, DUAL 9-BIT BOUNDARY SCAN TRANSCEIVER, INVERTED OUTPUT, PDSO56 |

| SN74LVTH18640DGGR | LVT SERIES, DUAL 9-BIT BOUNDARY SCAN TRANSCEIVER, INVERTED OUTPUT, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LVTH16835DLR | 功能描述:總線收發(fā)器 3.3V ABT 18-Bit Univ Bus Drvr W/3-St Otpt RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH16952DGGR | 功能描述:總線收發(fā)器 16bit ABT RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH16952DL | 功能描述:總線收發(fā)器 16bit ABT RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH16952DLG4 | 功能描述:總線收發(fā)器 10-Bit Buffer/Driver With 3-State Outputs RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH16952DLR | 功能描述:總線收發(fā)器 3.3 V ABT 16-Bit Reg Trncvr W/3-St Otpt RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。