- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97086 > SN74LVC544ADWR (TEXAS INSTRUMENTS INC) LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, INVERTED OUTPUT, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | SN74LVC544ADWR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, INVERTED OUTPUT, PDSO24 |

| 封裝: | PLASTIC, SO-24 |

| 文件頁數(shù): | 1/9頁 |

| 文件大小: | 127K |

| 代理商: | SN74LVC544ADWR |

SN74LVC544A

OCTAL REGISTERED TRANSCEIVER

WITH 3-STATE OUTPUTS

SCAS346E – MARCH 1994 – REVISED JUNE 1998

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

D EPIC (Enhanced-Performance Implanted

CMOS) Submicron Process

D Typical VOLP (Output Ground Bounce)

< 0.8 V at VCC = 3.3 V, TA = 25°C

D Typical VOHV (Output VOH Undershoot)

> 2 V at VCC = 3.3 V, TA = 25°C

D Power Off Disables Outputs, Permitting

Live Insertion

D Supports Mixed-Mode Signal Operation on

All Ports (5-V Input/Output Voltage With

3.3-V VCC)

D Package Options Include Plastic

Small-Outline (DW), Shrink Small-Outline

(DB), and Thin Shrink Small-Outline (PW)

Packages

description

This octal registered transceiver is designed for 1.65-V to 3.6-V VCC operation.

The SN74LVC544A contains two sets of D-type latches for temporary storage of data flowing in either direction.

Separate latch-enable (LEAB or LEBA) and output-enable (OEAB or OEBA) inputs are provided for each

register to permit independent control in either direction of data flow.

The A-to-B enable (CEAB) input must be low to enter data from A or to output data from B. If CEAB is low and

LEAB is low, the A-to-B latches are transparent; a subsequent low-to-high transition of LEAB places the A

latches in the storage mode. With CEAB and OEAB both low, the 3-state B outputs are active and reflect the

inverted data present at the output of the A latches. Data flow from B to A is similar to A to B, but requires using

the CEBA, LEBA, and OEBA.

To ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Inputs can be driven from either 3.3-V or 5-V devices. This feature allows the use of these devices as translators

in a mixed 3.3-V/5-V system environment.

The SN74LVC544A is characterized for operation from –40

°C to 85°C.

FUNCTION TABLE

INPUTS

OUTPUT

CEAB

LEAB

OEAB

A

B

H

X

Z

L

XH

X

Z

L

HL

X

B0

L

LL

L

H

L

H

L

A-to-B data flow is shown; B-to-A flow control is the

same except that it uses CEBA, LEBA, and OEBA.

Output level before the indicated steady-state input

conditions were established

PRODUCT

PREVIEW

Copyright

1998, Texas Instruments Incorporated

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

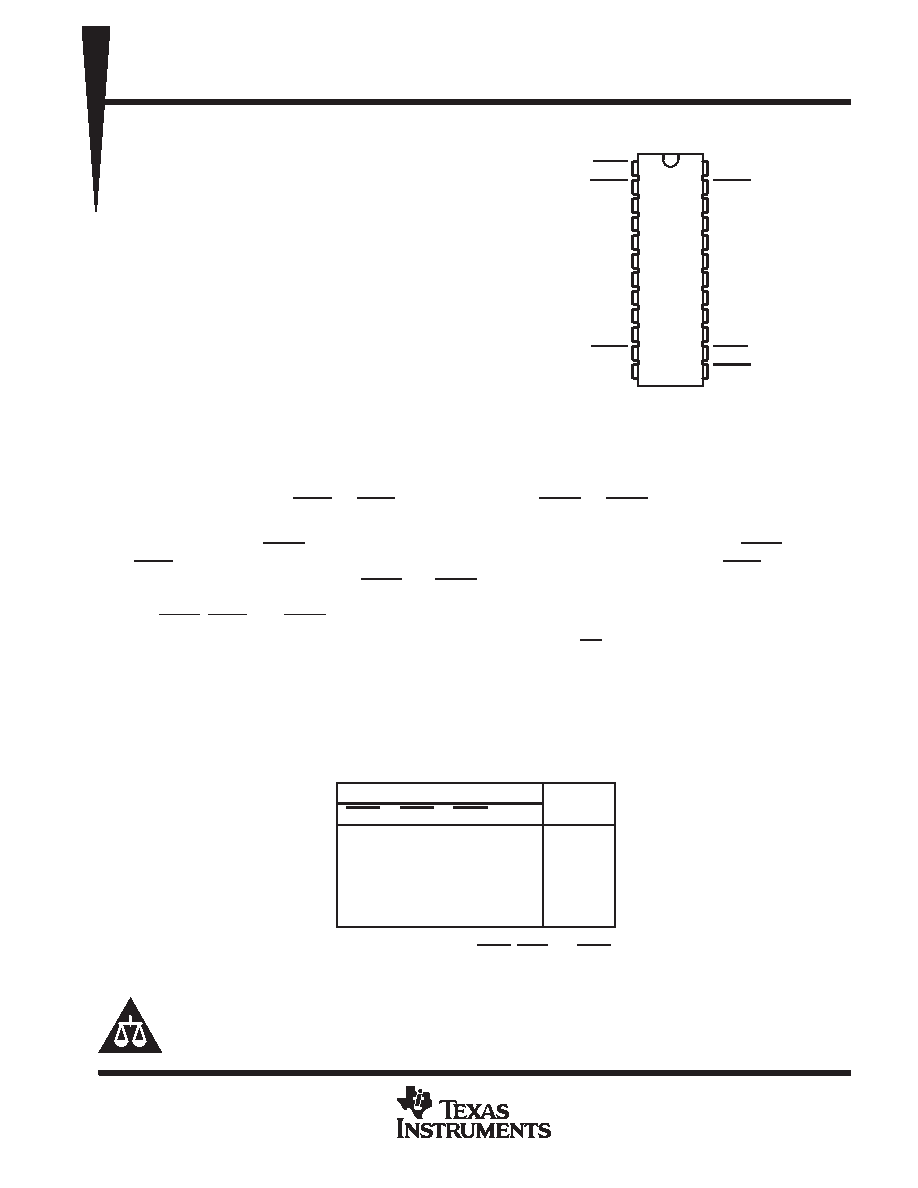

DB, DW, OR PW PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

LEBA

OEBA

A1

A2

A3

A4

A5

A6

A7

A8

CEAB

GND

VCC

CEBA

B1

B2

B3

B4

B5

B6

B7

B8

LEAB

OEAB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74LVC544DWR | LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, INVERTED OUTPUT, PDSO24 |

| SN74LVC573DBR | LVC/LCX/Z SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| SN74LVC573PWR | LVC/LCX/Z SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| SN74LVC646DBLE | LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO24 |

| SN74LVC646PW | LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LVC573ADBR | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74LVC573ADBRE4 | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74LVC573ADBRG4 | 功能描述:閉鎖 Octal Transp DType Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74LVC573ADGVR | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74LVC573ADGVRE4 | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。