- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98079 > SED1278F 16 X 40 DOTS DOT MAT LCD DSPL CTLR, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | SED1278F |

| 元件分類: | 顯示控制器 |

| 英文描述: | 16 X 40 DOTS DOT MAT LCD DSPL CTLR, PQFP80 |

| 封裝: | PLASTIC, QFP5-80 |

| 文件頁數(shù): | 7/13頁 |

| 文件大小: | 563K |

| 代理商: | SED1278F |

3

SED1278F/D

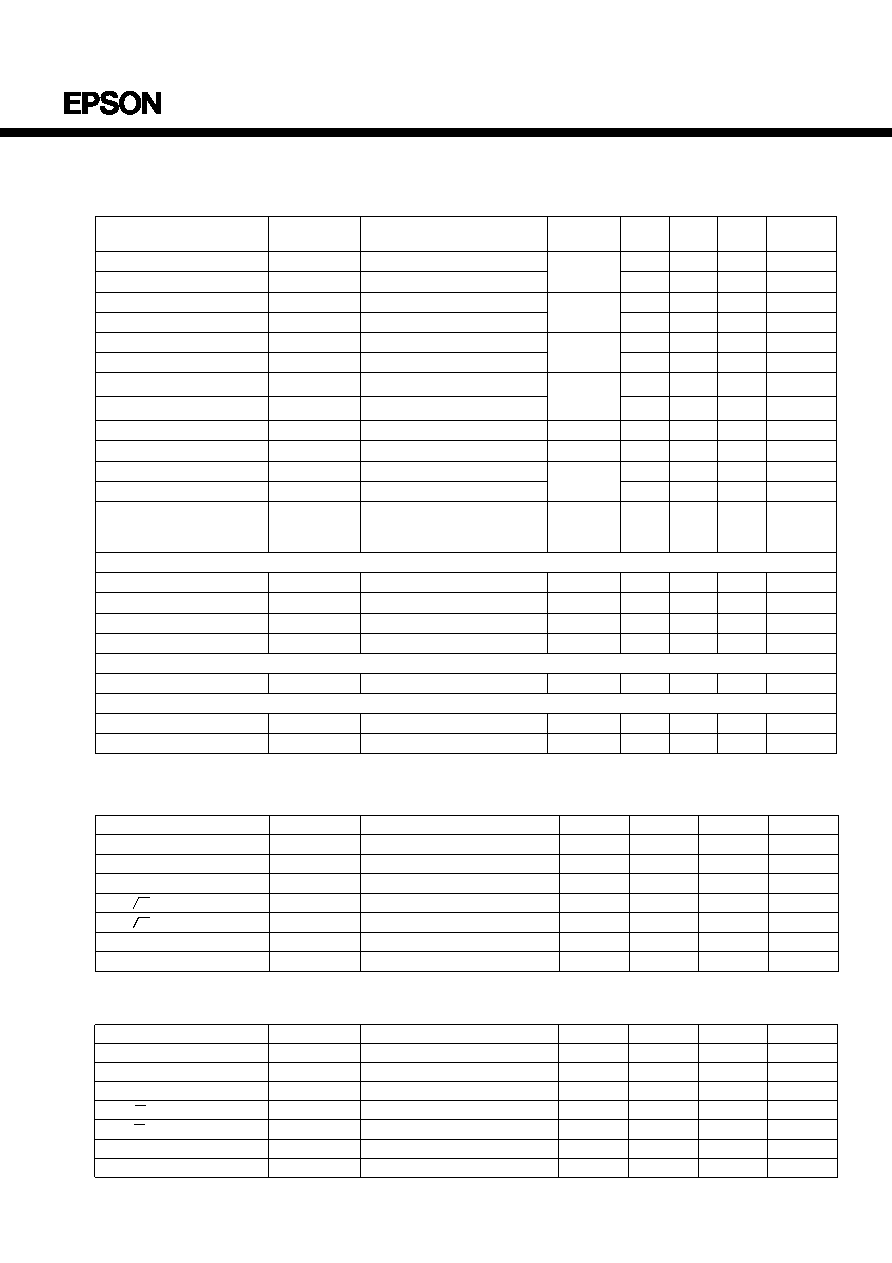

s ELECTRICAL CHARACTERISTICS

q DC Characteristics

r Write Cycle

VIH1

VIL1

VIH2

VIL2

VOH1

VOL1

VOH2

VOL2

RCOM

RSEG

IIL

—IP

IOP

fEXTCL

Duty

trEXTCL

tfEXTCL

fOSC

VLCD

Symbol

IOH = –0.205mA

IOL = 1.6mA

IOH = –0.04mA

IOL = 0.04mA

VCOM—Vn =0.5V

VSEG—Vn =0.5V

VI = 0 to VDD

VDD = 5V

Rf = 91K ±2%

Ceramic filter

VDD—V5

Condition

2.0

VSS

VDD—1.0

VSS

2.4

—

0.9VDD

—

50

—

125

45

—

190

245

3.0

Min.

DB0~DB7

RS, R/W, E

OSC1

DB0~DB7

VDD

COM1~16

SEG1~40

Applicable

Pin

—

2

2.5

—

125

250

50

—

270

250

—

0.5

Typ.

VDD

0.8

VDD

1.0

—

0.4

—

0.1VDD

10

1

250

350

55

0.2

350

255

VDD

0.8

Max.

V

k

k

A

mA

kHz

%

S

kHz

V

Unit

"H" level input voltage

(1)

"L" level input voltage

(1)

"H" level input voltage

(2)

"L" level input voltage

(2)

"H" level output voltage (1)

"L" level output voltage (1)

"H" level output voltage (2)

"L" level output voltage (2)

Driver-on resistor (COM)

Driver-on resistor (SEG)

I/O leakage current

Pull-up MOS current

Supply current

External clock operation

External clock operating frequency

External clock duty

External clock rise time

External clock fall time

Internal clock operation (Rf oscillation)

Oscillation frequency

Internal clock operation (Ceramic filter oscillation)

Oscillation frequency

LCD driving voltage

Characteristic

Rf oscillation, from

external clock

VDD = 5V, fosc = fCP = 270kHz

(VDD = 5.0V±10%, VSS = 0V, Ta = –20 to 75°C)

XSCL

LP

DO

q AC Characteristics

r Read Cycle

tcycE

tWEH

trE, tfE

tAS

tAH

tRD

tDHR

Symbol

500

220

—

40

10

—

20

Min.

—

Typ.

—

25

—

120

—

Max.

ns

Unit

CL = 100pF

Condition

Enable cycle time

Enable "H" level pulse width

Enable rise/fall time

RS, R W setup time

RS, R W address hold time

Read data output delay

Read data hold time

Characteristic

(VDD = 5.0V±10%, VSS = 0V, Ta = –20 to 75°C)

tcycE

tWEH

trE, tfE

tAS

tAH

tDS

tDH

Symbol

500

220

—

40

10

60

10

Min.

—

Typ.

—

25

—

Max.

ns

Unit

Condition

Enable cycle time

Enable "H" level pulse width

Enable rise/fall time

RS, R/W setup time

RS, R/W address hold time

Data setup time

Write data hold time

Characteristic

(VDD=5.0V

±10%, V

SS=0V, Ta=–20 to 75°C)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SED1330FBA | DOT MAT LCD DSPL CTLR, PQFP60 |

| SED1330FBB | 640 X 256 DOTS DOT MAT LCD DSPL CTLR, PQFP60 |

| SED1335FOA | DOT MAT LCD DSPL CTLR, PQFP60 |

| SED1336F0A | 640 X 256 DOTS DOT MAT LCD DSPL CTLR, PQFP60 |

| SED1345F0A | 640 X 480 DOTS CRT TO LCD CONV DSPL CTLR, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SED1278F0A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278F0B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278F0C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278F0D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278F0F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。