-

[北京]010-87982920

-

[深圳]0755-82701186

- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192656 > SD-14597D2-814Z (DATA DEVICE CORP) SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 PDF資料下載

參數(shù)資料

| 型號: | SD-14597D2-814Z |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 位置變換器 |

| 英文描述: | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| 封裝: | DDIP-36 |

| 文件頁數(shù): | 12/14頁 |

| 文件大?。?/td> | 416K |

| 代理商: | SD-14597D2-814Z |

INTERFACING - DIGITAL OUTPUTS AND CONTROLS

(CONTD)

DATA TRANSFERS

Digital output data from the SD-14595/96/97 can be transferred

to 8-bit and 16-bit bus systems. For 8-bit systems, the MSB and

LSB bytes are transferred sequentially. For 16-bit systems all

bits are transferred at the same time

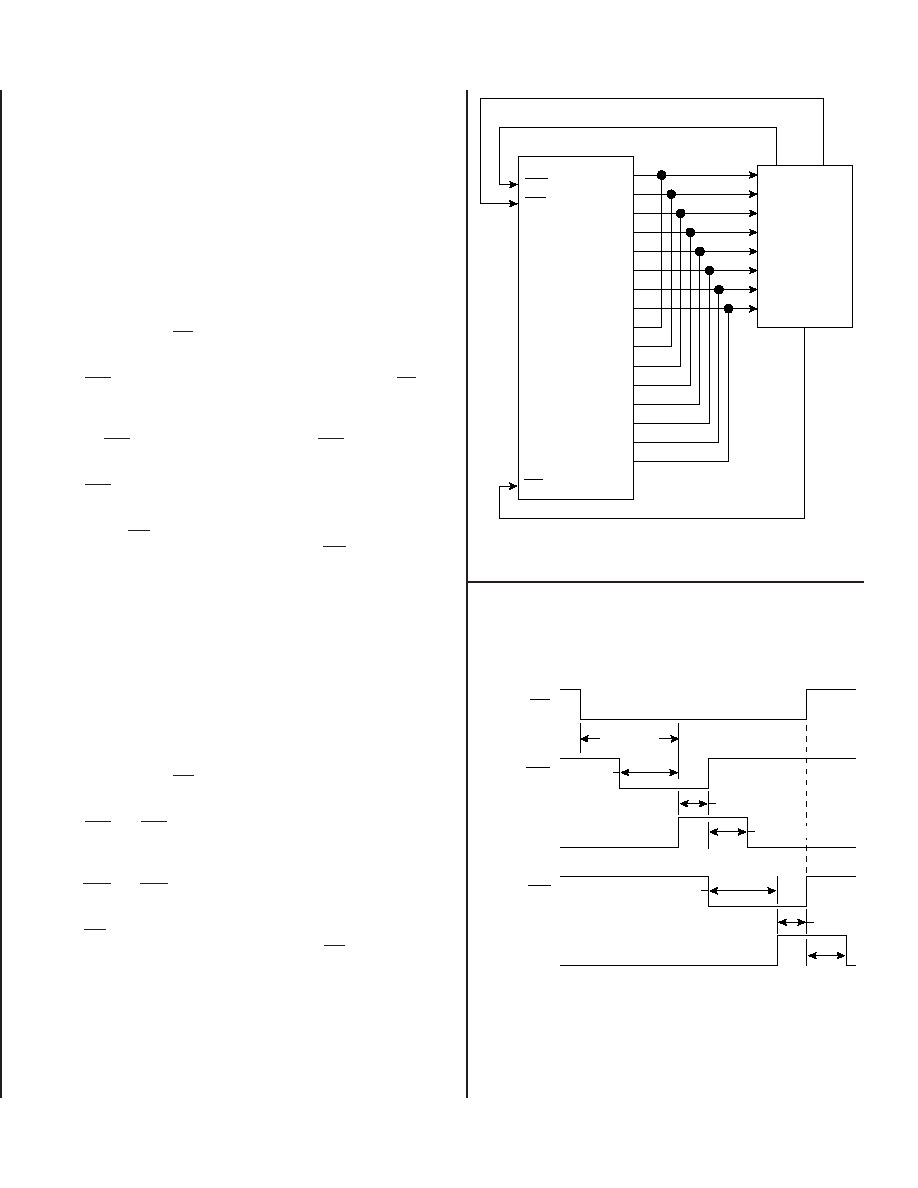

DATA TRANSFER TO 8-BIT BUS

FIGURES 11 and 12 show the connections and timing for trans-

ferring data from the SD-14595/96/97 to an 8-bit bus.

As can be seen by the timing diagram, the following occurs:

1. The converter INH control is applied and must remain low for

a minimum of 500 ns before valid data is transferred.

2. HBE is set to a low state (logic 0) 350 ns MIN after INH goes

low and must remain low for a minimum of 150 ns before the

MSB data (1-8) is valid and transferred.

3. As HBE is set to a high state (logic 1), LBE is brought low for

a 150 ns MIN before the LSB data is valid and transferred.

4. LBE should go high (to logic 1) at least 100 ns MAX before

another device uses the bus.

5.Setting INH high when data transfer is done, the data refresh

cycle can begin. Note the time it takes for INH to go to a logic 1

should be 100 ns minimum before valid data is transferred.

Note: For further understanding, refer to the beginning of this

section (Digital Interface, Digital Angle Outputs, Digital Angle

Output Timing, and Inhibit).

16-BIT DATA TRANSFER

Data transfer to the 16-bit bus is much simpler than the 8-bit bus.

FIGURES 13 and 14 (page 8) show the connections and timing

for transferring data from the SD-14595/96/97 to a 16-bit bus.

As can be seen by the timing diagram the following occurs:

1. The converter INH control is applied and must remain low for

a minimum of 500 ns before valid data is transferred.

2. HBE and LBE are set to a low state (logic 0) 350 ns MIN after

INH goes low and must remain low for a minimum of 150 ns

before the data (1-16) is valid and transferred.

3. HBE and LBE should go high (to logic 1) at least 100 ns MAX

before another device uses the bus.

4. INH goes high and data transfer is done and the data refresh

cycle can begin. Note the time it takes for INH to go to a logic 1

should be 100 ns minimum before valid data is transferred.

Note: For further understanding, refer to the beginning of this

section (Digital Interface, Digital Angle Outputs, Digital Angle

Output Timing, and Inhibit).

7

SD-14595/96/97

8-BIT BUS

(MSB) BIT 1

BIT 2

BIT 3

BIT 4

BIT 5

BIT 6

BIT 7

BIT 8

BIT 9

BIT 10

BIT 11

BIT 12

BIT 13

BIT 14

BIT 15

(LSB) BIT 16

D7

D6

D5

D4

D3

D2

D1

D0

HBE

LBE

INH

DATA 1-8

VALID

DATA 9-16

VALID

500 ns MIN

150 ns MIN

0 ns MIN

100 ns MAX

150 ns MIN

0 ns MIN

100 ns MAX

LBE

HBE

FIGURE 11. DATA TRANSFER TO 8-BIT BUS

FIGURE 12. DATA TRANSFER TO 8-BIT BUS TIMING

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SD-14597D2-814 | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14597D2-815K | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14597D2-815W | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14597D2-815Y | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14597D2-815 | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SD-14597D3-102 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14597D3-104 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14597D3-105 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14597D3-112 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14597D3-114 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。

- VIP會員服務(wù) |

- 廣告服務(wù) |

- 付款方式 |

- 聯(lián)系我們 |

- 招聘銷售 |

- 免責條款 |

- 網(wǎng)站地圖