- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192426 > SD-14531F3-404L (DATA DEVICE CORP) SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 PDF資料下載

參數(shù)資料

| 型號: | SD-14531F3-404L |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 位置變換器 |

| 英文描述: | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 |

| 封裝: | CERAMIC, FP-36 |

| 文件頁數(shù): | 9/16頁 |

| 文件大小: | 170K |

| 代理商: | SD-14531F3-404L |

2

Data

De

vice

Cor

por

ation

www

.d

dc-web.com

SD-14531

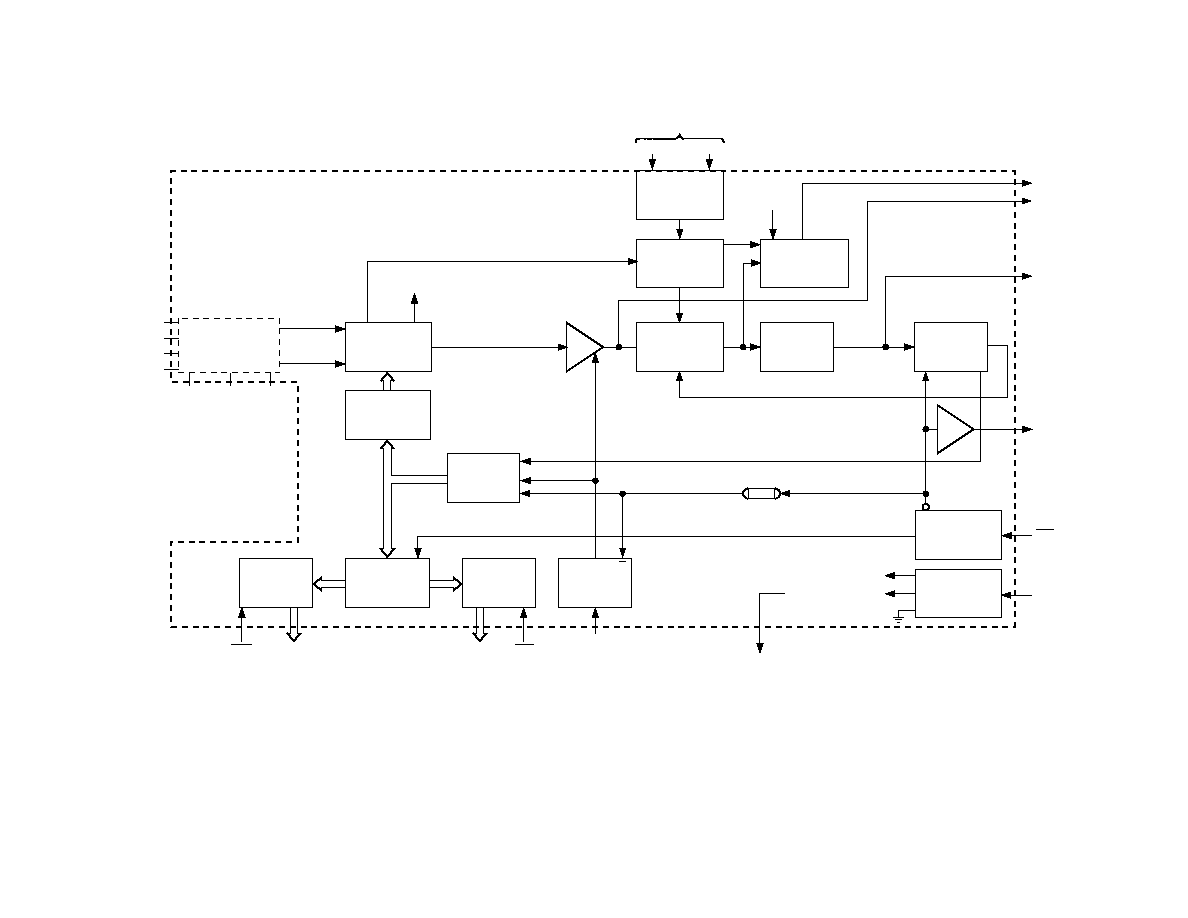

FIGURE 1. SD-14531 BLOCK DIAGRAM

HIGH

ACCURACY

CONTROL

TRANSFORMER

GAIN

DEMODULATOR

ERROR

PROCESSOR

VCO

16 BIT

UP/DOWN

COUNTER

U

T

VEL

D

SIN

(

θ-φ)

e

SIN

θ

COS

θ

3 STATE

TTL BUFFER

3 STATE

TTL BUFFER

VOLTAGE

DOUBLER

INHIBIT

TRANSPARENT

LATCH

16 BIT CT

TRANSPARENT

LATCH

16 BIT OUTPUT

TRANSPARENT

LATCH

EDGE

TRIGGERED

LATCH

DIGITAL

ANGLE

φ

Q

+8.6 V

S1

INH

BITS 1-8

HBE

50 ns DELAY

RESOLUTION

CONTROL

PROGRAMMABLE

SYNCHRO/

RESOLVER

CONDITIONER

1 LSB ANTIJITTER FEEDBACK

S

SR

R

S2

S3

S4

LOS

SYNTHESIZED

REF

REFERENCE

CONDITIONER

BIT DETECT

RH

RL

REF IN

LOS

ANALOG RETURN

V(+4.3 V)

V

+5 V

14B

LBE

BITS 9-16

T

U

INH

R

E

CB

VEL

e

BIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SD-14531F3-404Q | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 |

| SD-14531F3-404S | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 |

| SD-14531F3-404W | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 |

| SD-14531F3-404Y | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 |

| SD-14531F3-404Z | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDMA36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SD1455 | 功能描述:射頻雙極電源晶體管 NPN 25V 170-230MHz RoHS:否 制造商:M/A-COM Technology Solutions 配置:Single 直流集電極/Base Gain hfe Min:40 最大工作頻率:30 MHz 集電極—發(fā)射極最大電壓 VCEO:25 V 發(fā)射極 - 基極電壓 VEBO:4 V 集電極連續(xù)電流:20 A 最大直流電集電極電流: 功率耗散:250 W 封裝 / 箱體:Case 211-11 封裝:Tray |

| SD1456 | 功能描述:射頻雙極電源晶體管 NPN 28V 170-230MHz RoHS:否 制造商:M/A-COM Technology Solutions 配置:Single 直流集電極/Base Gain hfe Min:40 最大工作頻率:30 MHz 集電極—發(fā)射極最大電壓 VCEO:25 V 發(fā)射極 - 基極電壓 VEBO:4 V 集電極連續(xù)電流:20 A 最大直流電集電極電流: 功率耗散:250 W 封裝 / 箱體:Case 211-11 封裝:Tray |

| SD1457 | 功能描述:射頻放大器 RF Bipolar Trans RoHS:否 制造商:Skyworks Solutions, Inc. 類型:Low Noise Amplifier 工作頻率:2.3 GHz to 2.8 GHz P1dB:18.5 dBm 輸出截獲點:37.5 dBm 功率增益類型:32 dB 噪聲系數(shù):0.85 dB 工作電源電壓:5 V 電源電流:125 mA 測試頻率:2.6 GHz 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-16 封裝:Reel |

| SD1458 | 功能描述:射頻放大器 RF Bipolar Trans RoHS:否 制造商:Skyworks Solutions, Inc. 類型:Low Noise Amplifier 工作頻率:2.3 GHz to 2.8 GHz P1dB:18.5 dBm 輸出截獲點:37.5 dBm 功率增益類型:32 dB 噪聲系數(shù):0.85 dB 工作電源電壓:5 V 電源電流:125 mA 測試頻率:2.6 GHz 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-16 封裝:Reel |

| SD1459 | 功能描述:射頻雙極電源晶體管 NPN 28V 170-230MHz RoHS:否 制造商:M/A-COM Technology Solutions 配置:Single 直流集電極/Base Gain hfe Min:40 最大工作頻率:30 MHz 集電極—發(fā)射極最大電壓 VCEO:25 V 發(fā)射極 - 基極電壓 VEBO:4 V 集電極連續(xù)電流:20 A 最大直流電集電極電流: 功率耗散:250 W 封裝 / 箱體:Case 211-11 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。