- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385820 > SCN2661BC1F28 (NXP SEMICONDUCTORS) Enhanced programmable communications interface EPCI PDF資料下載

參數(shù)資料

| 型號(hào): | SCN2661BC1F28 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Enhanced programmable communications interface EPCI |

| 中文描述: | 1 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, CDIP28 |

| 封裝: | 0.600 INCH, CERAMIC, DIP-28 |

| 文件頁數(shù): | 6/19頁 |

| 文件大?。?/td> | 131K |

| 代理商: | SCN2661BC1F28 |

Philips Semiconductors

Product specification

SCN2661/SCN68661

Enhanced programmable communications

interface (EPCI)

1994 Apr 27

6

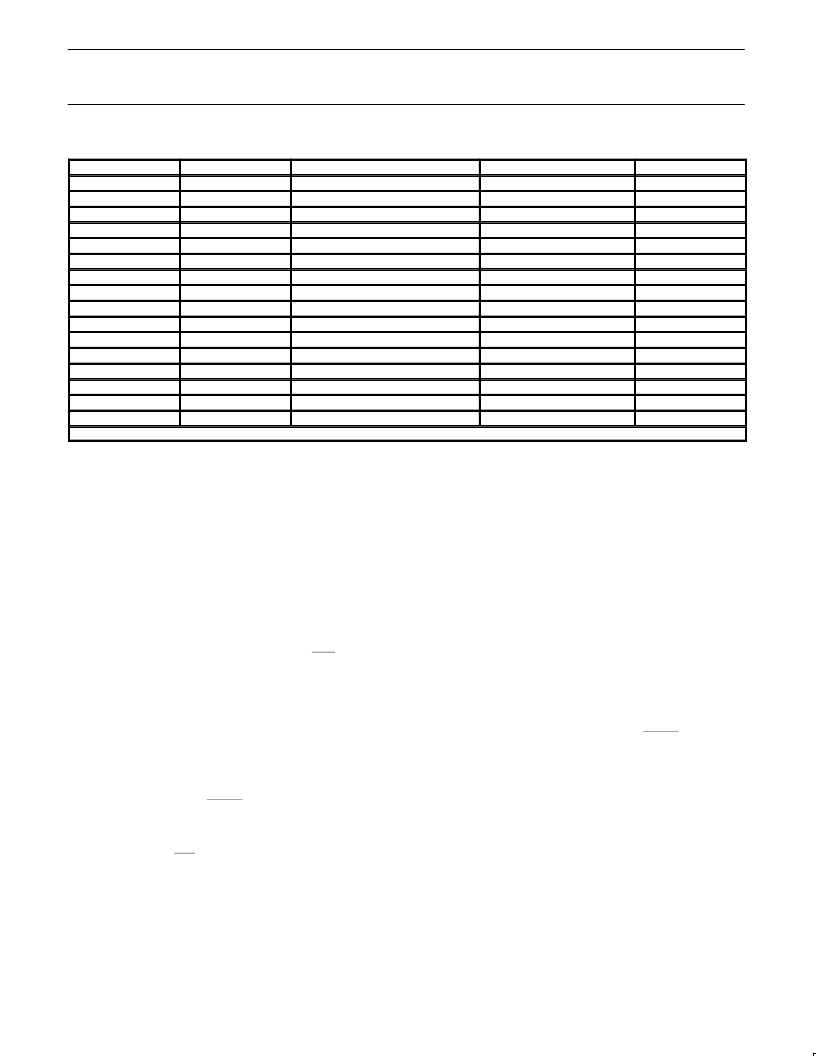

68661C (BRCLK = 5.0688MHz)

MR23–20

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

NOTE:

16X clock is used in asynchronous mode. In synchronous mode, clock multiplier is 1X and BRG can be used only for TxC.

BAUD RATE

50

75

110

134.5

150

300

600

1200

1800

2000

2400

3600

4800

7200

9600

19200

ACTUAL FREQUENCY 16X CLOCK

0.8kHz

1.2

1.76

2.1523

2.4

4.8

9.6

19.2

28.8

32.081

38.4

57.6

76.8

115.2

153.6

316.8

PERCENT ERROR

—

—

—

0.016

—

—

—

—

—

0.253

—

—

—

—

—

3.125

DIVISOR

6336

4224

2880

2355

2112

1056

528

264

176

158

132

88

66

44

33

16

OPERATION

The functional operation of the 68661 is programmed by a set of

control words supplied by the CPU. These control words specify

items such as synchronous or asynchronous mode, baud rate,

number of bits per character, etc. The programming procedure is

described in the EPCI programming section of the data sheet.

After programming, the EPCI is ready to perform the desired

communications functions. The receiver performs serial to parallel

conversion of data received from a modem or equivalent device.

The transmitter converts parallel data received from the CPU to a

serial bit stream. These actions are accomplished within the

framework specified by the control words.

Receiver

The 68661 is conditioned to receiver data when the DCD input is

Low and the RxEN bit in the commands register is true. In the

asynchronous mode, the receiver looks for High-to-Low (mark to

space) transition of the start bit on the RxD input line. If a transition

is detected, the state of the RxD line is sampled again after a delay

of one-half of a bit-time. If RxD is now high, the search for a valid

start bit is begun again. If RxD is still Low, a valid start bit is

assumed and the receiver continues to sample the input line at one

bit time intervals until the proper number of data bits, the parity bit,

and one stop bit have been assembled. The data are then

transferred to the receive data holding register, the RxRDY bit in the

status register is set, and the RxRDY output is asserted. If the

character length is less than 8 bits, the High order unused bits in the

holding register are set to zero. The parity error, framing error, and

overrun error status bits are strobed into the status register on the

positive going edge of RxC corresponding to the received character

boundary. If the stop bit is present, the receiver will immediately

begin its search for the next start bit. If the stop bit is absent

(framing error), the receiver will interpret a space as a start bit if it

persists into the next bit timer interval. If a break condition is

detected (RxD is Low for the entire character as well as the stop bit),

only one character consisting of all zeros (with the FE status bit SR5

set) will be transferred to the holding register. The RxD input must

return to a High condition before a search for the next start bit

begins.

Pin 25 can be programmed to be a break detect output by

appropriate setting of MR27-MR24. If so, a detected break will

cause that pin to go High. When RxD returns to mark for one RxC

time, pin 25 will go low. Refer to the Break Detection Timing

Diagram.

When the EPCI is initialized into the synchronous mode, the

receiver first enters the hunt mode on a 0 to 1 transition of RxEN

(CR2). In this mode, as data are shifted into the receiver shift

register a bit at a time, the contents of the register are compared to

the contents of the SYN1 register. If the two are not equal, the next

bit is shifted in and the comparison is repeated. When the two

registers match, the hunt mode is terminated and character

assembly mode begins. If single SYN operation is programmed, the

SYN DETECT status bit is set. If double SYN operation is

programmed, the first character assembled after SYN1 must be

SYN2 in order for the SYN DETECT bit to be set. Otherwise, the

EPCI returns to the hunt mode. (Note that the sequence

SYN1-SYN1-SYN2 will not achieve synchronization.) When

synchronization has been achieved, the EPCI continues to

assemble characters and transfer then to the holding register,

setting the RxRDY status bit and asserting the RxRDY output each

time a character is transferred. The PE and OE status bits are set

as appropriate. Further receipt of the appropriate SYN sequence

sets the SYN DETECT status bit. If the SYN stripping mode is

commanded, SYN characters are not transferred to the holding

register. Note that the SYN characters used to establish initial

synchronization are not transferred to the holding register in any

case.

External jam synchronization can be achieved via pin 9 by

appropriate setting of MR27-MR24. When pin 9 is an XSYNC input,

the internal SYN1, SYN1–SYN2, and DLE–SYN1 detection is

disabled. Each positive going signal on XSYNC will cause the

receiver to establish synchronization on the rising edge of the next

RxC pulse. Character assembly will start with the RxD input at this

edge. XSYNC may be lowered on the next rising edge of RxD. This

external synchronization will cause the SYN DETECT status bit to

be set until the status register is read. Refer to XSYNC timing

diagram.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCN2661BC1N28 | SM Series Subminiature Basic Switch, Single Pole Double Throw (SPDT), 250 Vac, 5 A, Pin Plunger Actuator, Solder Termination |

| SCN2661CA1F28 | SM Series Subminiature Basic Switch, Single Pole Double Throw (SPDT), 250 Vac, 5 A, Pin Plunger Actuator, Solder Termination |

| SCN2661CC1A28 | Enhanced programmable communications interface EPCI |

| SCN2661CC1F28 | SM Series Subminiature Basic Switch, Single Pole Double Throw (SPDT), 125 Vac, 1 A, Pin Plunger Actuator, Solder Termination |

| SCN2661CC1N28 | Enhanced programmable communications interface EPCI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCN2661BC1N28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced programmable communications interface EPCI |

| SCN2661CA1F28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced programmable communications interface EPCI |

| SCN2661CC1A28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced programmable communications interface EPCI |

| SCN2661CC1F28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced programmable communications interface EPCI |

| SCN2661CC1N28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced programmable communications interface EPCI |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。