- 您現(xiàn)在的位置:買賣IC網 > PDF目錄385814 > SAA7388 (NXP Semiconductors N.V.) Error correction and host interface IC for CD-ROM ELM PDF資料下載

參數(shù)資料

| 型號: | SAA7388 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Error correction and host interface IC for CD-ROM ELM |

| 中文描述: | 錯誤更正和主機接口集成電路的CD - ROM榆木 |

| 文件頁數(shù): | 17/60頁 |

| 文件大小: | 226K |

| 代理商: | SAA7388 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

1996 Apr 26

17

Philips Semiconductors

Preliminary specification

Error correction and host interface IC for

CD-ROM (ELM)

SAA7388

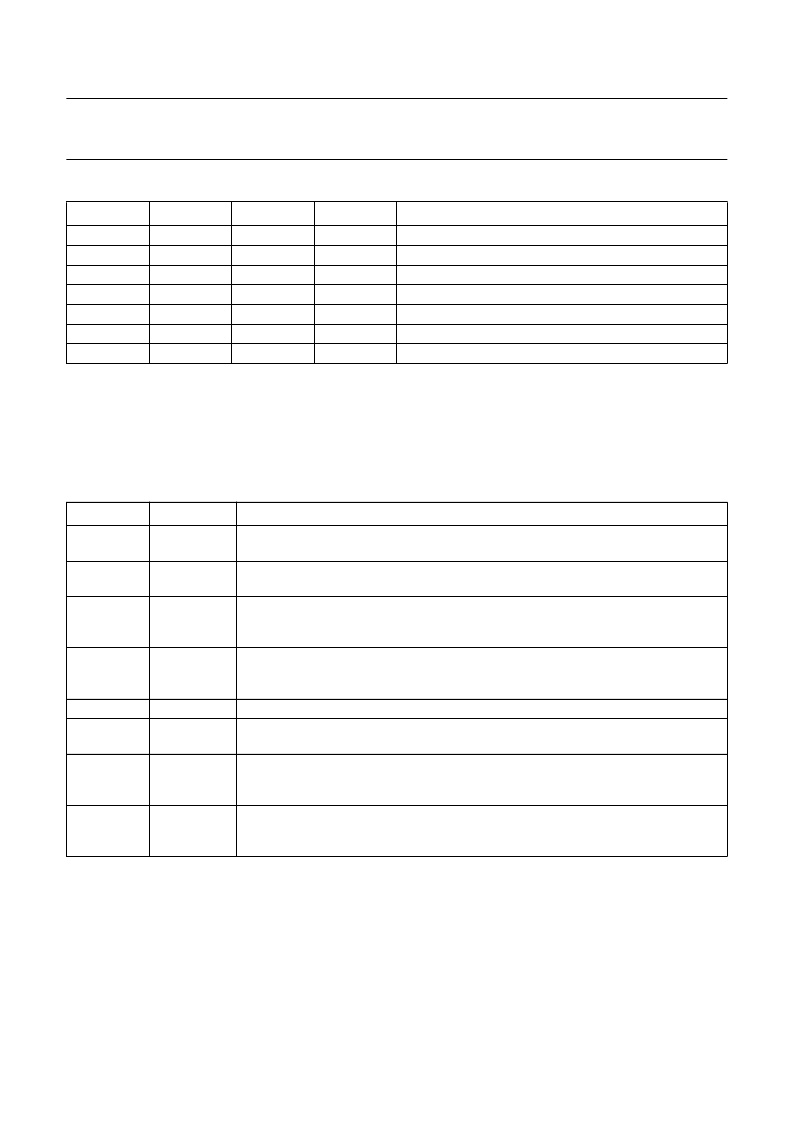

Table 7

Error correction modes

Note

1.

Where X = don’t care.

7.7.13

CTRL1

The reset function clears all the flags in this register.

Table 8

CTRL1 register bits

DECEN

lookahead

WRRQ

ECCRQ

decoder mode

0

1

1

1

1

1

1

X

0

0

0

0

1

1

X

0

0

1

1

1

1

X

0

1

0

1

0

1

decoder disable; note 1

monitor only

repeat correction

write only

real-time correct, normal mode

write only, lookahead

real-time correct, lookahead

BIT

NAME

FUNCTION

7

SYIEN

Disable sync interpolation = 0; Enable sync interpolation = 1. Enabling SYIEN prevents

loss of synchronization when an error occurs in a sync pattern during data read.

Disable sync detection = 0; Enable sync detection = 1. Enabling SYDEN synchronizes

the decoder with the sync pattern detected in the input data.

Descramble disable (audio) = 0; Descramble enable = 1. This bit enables/disables

descrambling. Setting this bit to logic 0 allows reading of raw data on disc, even audio

signals. This bit should be set to logic 1 for CROM data.

CRC with error correction disabled = 0; Detection errors are corrected = 1. This bit

enables/disables rewriting of error bytes in the buffer during error correction. Setting

the bit to logic 0 allows CRC checks without error correction.

Mode 1 request = 0; Mode 2 request = 1. This bit discriminates Mode 1/Mode 2.

Form 1 request = 0; Form 2 request = 1. This bit discriminates Mode 2/Form 1 and

Mode 2/Form 2.

Disable mode check function = 0; Enable mode check function = 1. If the mode

specified in the mode byte does not correspond with the raw data mode bit and this bit

is set to logic 1 then error correction and detection is disabled.

Header data on registers Head0 to Head3 = 0; Sub-header data on registers

Head0 to Head3 = 1. This bit toggles header and sub-header data between registers

HEAD0 to HEAD3.

6

SYDEN

5

DSCREN

4

COWREN

3

2

MODRQ

FORMRQ

1

MBCKRQ

0

SHDREN

相關PDF資料 |

PDF描述 |

|---|---|

| SAA7392HL | Channel encoder/decoder CDR60 |

| SAA7392 | Channel encoder/decoder CDR60(通道編碼器/譯碼器) |

| SAA7705H | Car radio Digital Signal Processor(DSP)(車載電臺數(shù)字信號處理器) |

| SAA7712H | Sound effects DSP(聲音效應數(shù)字信號處理器) |

| SAA7712 | Sound effects DSP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7388GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7390 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

| SAA7390GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

| SAA7391 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7391H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復。