- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192297 > S29GL032M10BAIR43 (SPANSION LLC) MirrorBit Flash Family PDF資料下載

參數(shù)資料

| 型號(hào): | S29GL032M10BAIR43 |

| 廠商: | SPANSION LLC |

| 元件分類: | PROM |

| 英文描述: | MirrorBit Flash Family |

| 中文描述: | 2M X 16 FLASH 3V PROM, 100 ns, PBGA48 |

| 封裝: | 8 X 9 MM, FBGA-48 |

| 文件頁數(shù): | 34/116頁 |

| 文件大小: | 6024K |

| 代理商: | S29GL032M10BAIR43 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

22

S29GL-M MirrorBitTM Flash Family

S29GL-M_00_B8 February 7, 2007

Data

Sheet

Device Bus Operations

This section describes the requirements and use of the device bus operations, which are initiated

through the internal command register. The command register itself does not occupy any addres-

sable memory location. The register is a latch used to store the commands, along with the

address and data information needed to execute the command. The contents of the register serve

as inputs to the internal state machine. The state machine outputs dictate the function of the de-

vice. Table 5 lists the device bus operations, the inputs and control levels they require, and the

resulting output. The following subsections describe each of these operations in further detail.

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 11.5–12.5 V,

VHH = 11.5 V – 12.5 V, X = Don’t Care, SA = Sector Address, AIN = Address In,

DIN = Data In, DOUT = Data Out

Notes:

1. Addresses are Amax:A0 in word mode; Amax:A-1 in byte mode. Sector addresses are Amax:A15

in both modes.

2. The sector protect and sector unprotect functions may also be implemented via programming

equipment. See the “Sector Group Protection and Unprotection” section.

3. If WP# = VIL, the first or last sector remains protected (for uniform sector devices), and the two

outer boot sectors are protected (for boot sector devices). If WP# = VIH, the first or last sector, or

the two outer boot sectors are protected or unprotected as determined by the method described in

“Sector Group Protection and Unprotection”. All sectors are unprotected when shipped from the

factory (The Secured Silicon Sector may be factory protected depending on version ordered.)

4. DIN or DOUT as required by command sequence, data polling, or sector protect algorithm (see

Word/Byte Configuration

The BYTE# pin controls whether the device data I/O pins operate in the byte or word configura-

tion. If the BYTE# pin is set at logic ‘1’, the device is in word configuration, DQ0–DQ15 are active

and controlled by CE# and OE#.

If the BYTE# pin is set at logic ‘0’, the device is in byte configuration, and only data I/O pins DQ0–

DQ7 are active and controlled by CE# and OE#. The data I/O pins DQ8–DQ14 are tri-stated, and

the DQ15 pin is used as an input for the LSB (A-1) address function.

Requirements for Reading Array Data

To read array data from the outputs, the system must drive the CE# and OE# pins to VIL. CE# is

the power control and selects the device. OE# is the output control and gates array data to the

output pins. WE# should remain at VIH.

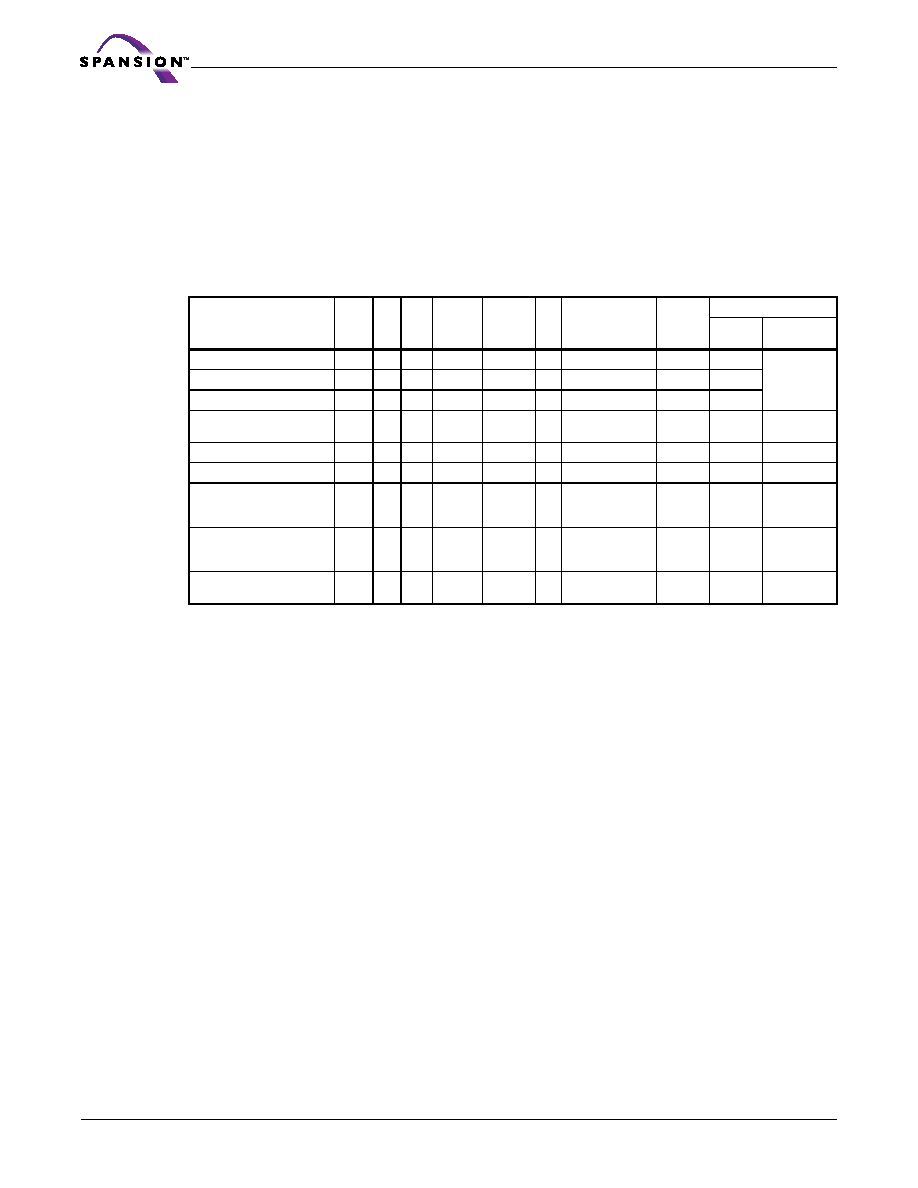

Table 5. Device Bus Operations

Operation

CE#

OE

#

WE# RESET#

WP#

AC

C

Addresses

DQ0–

DQ7

DQ8–DQ15

BYTE#

= VIH

BYTE#

= VIL

Read

LL

H

X

AIN

DOUT

DQ8–DQ14

= High-Z,

DQ15 = A-1

Write (Program/Erase)

LH

L

H

AIN

Accelerated Program

LH

L

H

AIN

Standby

VCC ±

0.3 V

XX

VCC ±

0.3 V

X

H

X

High-Z

Output Disable

L

H

X

High-Z

Reset

X

L

X

High-Z

Sector Group Protect

LH

L

VID

HX

SA, A6 =L,

A3=L, A2=L,

A1=H, A0=L

X

Sector Group Unprotect

LH

L

ID

HX

SA, A6=H,

A3=L, A2=L,

A1=H, A0=L

X

Temporary Sector

Group Unprotect

XX

X

VID

HX

AIN

(Note 4)(Note 4)High-Z

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S29GL032M10BFIR42 | MirrorBit Flash Family |

| S29GL032M10BFIR32 | T528 Series - I, M, Z Case Sizes - Face Down Termination Tantalum Surface Mount Capacitor; Capacitance [nom]: 330uF; Working Voltage (Vdc)[max]: 4V; Capacitance Tolerance: +/-20%; Dielectric: Tantalum, Solid; ESR: 9.0mΩ; Lead Style: Surface-Mount Chip; Lead Dimensions: 7343-17; Termination: 100% Tin (Sn); Body Dimensions: 7.3mm x 4.3mm x 1.7mm; Temperature Range: -55C to +105C; Container: Tape & Reel; Qty per Container: 1,000; Features: Face Down Termination |

| S29GL032M10BFIR40 | MirrorBit Flash Family |

| S29GL032M10TAIR00 | MirrorBit Flash Family |

| S29GL032M10TAIR03 | MirrorBit Flash Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S29GL032M10BAIR50 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:MirrorBit Flash Family |

| S29GL032M10BAIR52 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:MirrorBit Flash Family |

| S29GL032M10BAIR53 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:MirrorBit Flash Family |

| S29GL032M10BAIR60 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:MirrorBit Flash Family |

| S29GL032M10BAIR62 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:MirrorBit Flash Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。