- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374648 > S25FL001D0FMFI003 (SPANSION LLC) 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface PDF資料下載

參數(shù)資料

| 型號(hào): | S25FL001D0FMFI003 |

| 廠商: | SPANSION LLC |

| 元件分類: | DRAM |

| 英文描述: | 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| 中文描述: | 1M X 1 SPI BUS SERIAL EEPROM, PDSO8 |

| 封裝: | 0.150 INCH, LEAD FREE, PLASTIC, MS-012AA, SO-8 |

| 文件頁(yè)數(shù): | 14/38頁(yè) |

| 文件大小: | 892K |

| 代理商: | S25FL001D0FMFI003 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

14

S25FL Family (Serial Peripheral Interface)

30167A+1 June 9, 2004

P r e l i m i n a r y I n f o r m a t i o n

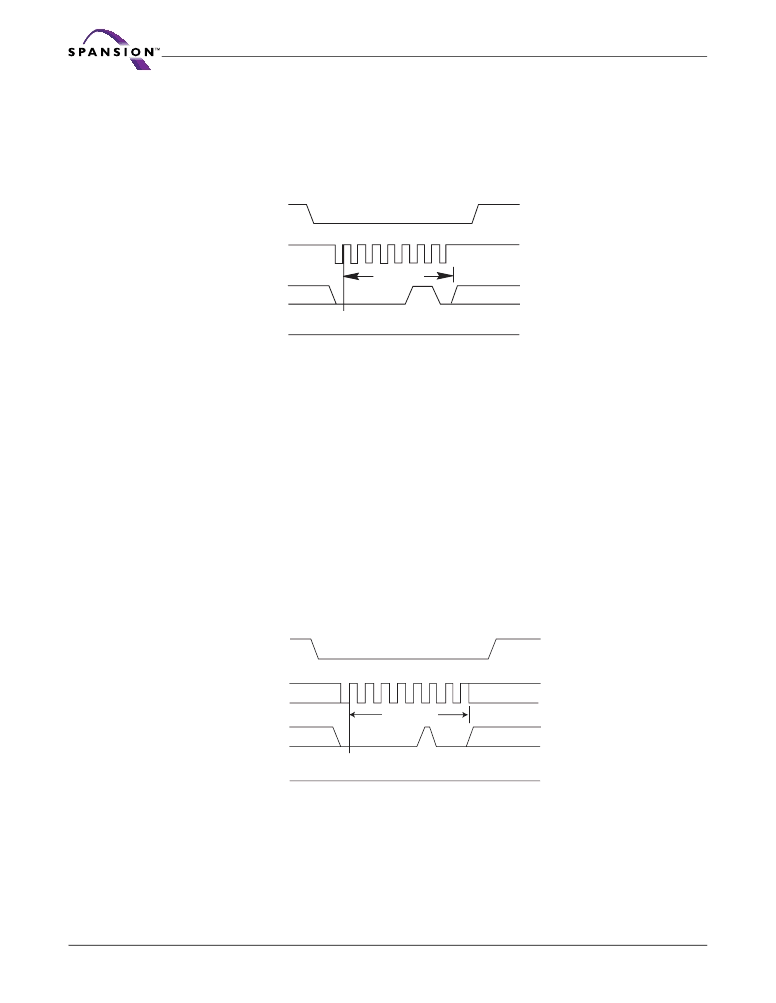

Write Enable (WREN)

The Write Enable (WREN) instruction (

Figure 4

) sets the Write Enable Latch (WEL)

bit. The Write Enable Latch (WEL) bit must be set prior to every Page Program

(PP), Erase (SE or BE) and Write Status Register (WRSR) instruction. The Write

Enable (WREN) instruction is entered by driving Chip Select (CS#) Low, sending

the instruction code, and then driving Chip Select (CS#) High.

Figure 4. Write Enable (WREN) Instruction Sequence

Write Disable (WRDI)

The Write Disable (WRDI) instruction (

Figure 5

) resets the Write Enable Latch

(WEL) bit. The Write Disable (WRDI) instruction is entered by driving Chip Select

(CS#) Low, sending the instruction code, and then driving Chip Select (CS#)

High.

The Write Enable Latch (WEL) bit is reset under the following conditions:

Power-up

Write Disable (WRDI) instruction completion

Write Status Register (WRSR) instruction completion

Page Program (PP) instruction completion

Sector Erase (SE) instruction completion

Bulk Erase (BE) instruction completion

Figure 5. Write Disable (WRDI) Instruction Sequence

Read Status Register (RDSR)

The Read Status Register (RDSR) instruction allows the Status Register to be

read. The Status Register may be read at any time, even while a Program, Erase,

or Write Status Register cycle is in progress. When one of these cycles is in

progress, it is recommended to check the Write In Progress (WIP) bit before

CS#

SCK

SI

SO

High Impedance

Instruction

0 1

2

3

4

5 6

7

0

1 2

3 4 5

6 7

SCK

SI

SO

High Impedance

Instruction

CS#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S25FL001D0FMFI011 | 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FMFI013 | INDUCTOR,STANDARD WOUND,0806,47UH 10% ,T&R RoHS Compliant: Yes |

| S25FL001D0FNAI001 | 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNAI003 | 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNAI011 | 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S25FL001D0FMFI011 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FMFI013 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNAI001 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNAI003 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNAI011 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。