- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373274 > RIVA128ZX (意法半導(dǎo)體) 128-BIT 3D MULTIMEDIA ACCELERATOR PDF資料下載

參數(shù)資料

| 型號: | RIVA128ZX |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 128-BIT 3D MULTIMEDIA ACCELERATOR |

| 中文描述: | 128位3D多媒體加速器 |

| 文件頁數(shù): | 8/85頁 |

| 文件大小: | 609K |

| 代理商: | RIVA128ZX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

128-BIT 3D MULTIMEDIA ACCELERATOR

RIVA128ZX

8/85

2.5

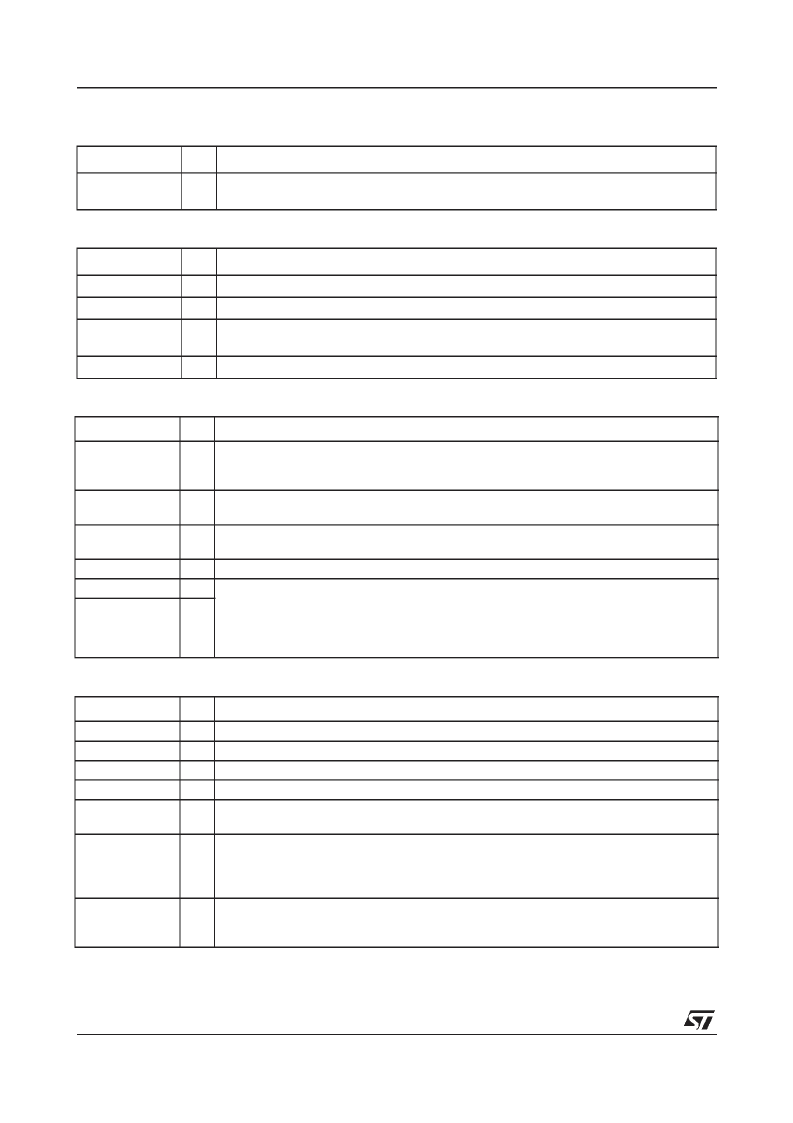

DEVICE ENABLE SIGNALS

2.6

DISPLAY INTERFACE

2.7

VIDEO DAC AND PLL ANALOG SIGNALS

2.8

POWER SUPPLY

Signal

I/O

Description

ROMCS#

O

Enables reads from an external 64Kx 8 or 32Kx8 ROM or Flash ROM. This signal is used

in conjunction with framebuffer data lines as described abovein Section 2.3.

Signal

I/O

Description

SDA

I/O

Used for DDC2B+ monitor communication and interface to video decoder devices.

SCL

I/O

Used for DDC2B+ monitor communication and interface to video decoder devices.

VIDVSYNC

O

Vertical sync supplied to the display monitor.No bufferingis required. In TV mode this sig-

nal supplies composite sync to an external PAL/NTSCencoder.

VIDHSYNC

O

Horizontal sync supplied to the display monitor. No buffering is required.

Signal

I/O

Description

RED,

GREEN,

BLUE

COMP

O

RGB display monitor outputs. These are software configurableto drive either a doubly ter-

minated or singly terminated 75

load.

-

External compensation capacitor for the video DACs. This pin should be connected to

DACVDD

via the compensation capacitor, see Figure 66, page 60.

A precision resistor placed between this pin and GND sets the full-scale video DAC cur-

rent, see Figure 66, page 60.

A capacitor should be placed between this pin and GND as shown in Figure 66, page 60.

A series resonant crystal is connected between these two points to provide the reference

clock for the internal MCLK and VCLK clock synthesizers,see Figure 66 and Table20,

page 60. Alternately, an external LVTTLclock oscillator output may be driven into

XTA-

LOUT

, connecting

XTALIN

to GND. For designs supporting TV-out,

XTALOUT

should be

driven by a referenceclock as described in Section 11.6, page 61.

RSET

-

VREF

XTALIN

XTALOUT

-

I

O

Signal

I/O

Description

DACVDD

PLLVDD

VDD

GND

MPCLAMP

P

P

P

P

P

Analog power supply for the video DACs.

Analog power supply for all clock synthesizers.

Digital power supply.

Ground.

MPCLAMP

is connected to +5V to protect the 3.3V RIVA128ZXfrom external devices

which will potentially drive 5V signal levelsonto the Video Port input pins.

HOSTVDD

is connected to the Vddq 3.3 pins on the AGP connector. This is the supply

voltage for the I/O buffersand is isolated from the core VDD.On AGP designs these pins

are also connected to the

HOSTCLAMP

pins. On PCI designs they are connected to the

3.3V supply.

HOSTCLAMP

is the supply signalling rail protection for the host interface. In AGPdesigns

these signals are connected to Vddq 3.3. For PCI designs they are connected to the I/O

power pins (V

(I/O)

).

HOSTVDD

P

HOSTCLAMP

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RIVA128 | RIVA 128⑩ 128-BIT 3D MULTIMEDIA ACCELERATOR |

| RIX-0142-H | FILTER IEC EINGANG ULTRA KOMPAKT 1A |

| RIX-0342-H | FILTER IEC EINGANG ULTRA KOMPAKT 3A |

| RIX-0642-H | FILTER IEC EINGANG ULTRA KOMPAKT 6A |

| RJ45SRB-BLACK | TUELLE FUER RJ45 STECKER SW Inhalt pro Packung: 8 Stk. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RIVCF256H | 制造商:STEC Inc 功能描述:256MB COMPACT FLASH - Bulk |

| RIVET DPG FLOAT MTG | 制造商:ITT Interconnect Solutions 功能描述:Rack & Panel |

| RIVET(SSR389) | 制造商: 功能描述: 制造商:undefined 功能描述: |

| RIVET-DPD-PIN-INSERT-SPCR | 制造商:ITT Interconnect Solutions 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。