- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373274 > RISC Unifying RISC and DSP PDF資料下載

參數(shù)資料

| 型號: | RISC |

| 英文描述: | Unifying RISC and DSP |

| 中文描述: | 統(tǒng)一的RISC和DSP |

| 文件頁數(shù): | 4/7頁 |

| 文件大?。?/td> | 176K |

| 代理商: | RISC |

Hyperstone E1-32X/E1-16X RISC/DSP

· 32-bit RISC/DSP processor

· Parallelism of ALU, DSP unit and

Load/Store unit

· 16, 32, 48-bit instructions

· 64 local, 26 global registers

· Local regs organized in circular

register stack with stack frames

· 4 GByte memory address space

· Separate I/O address space

· 8 kByte RAM on-chip (1 cycle)

· On-chip instruction cache

· Separate address and data bus

· 32-bit timer and watchdog timer

· Comprehensive DRAM controller

· Programmable bus timing for all

memory and I/O devices

· Clock frequency up to 80 MHz

· On-chip PLL (4:1)

· Static design

· 80 MIPS, up to 240 MOPS

· Up to 700 MIPS/Watt

· 1 k complex FFT in less than 0.5 ms

· 1 cycle MPY (16 x 16 bit)

· 4 cycle MPY (32 x 32 bit)

· 1 cycle multiply-add (pipelined)

· 1 cycle MOV, ADD, CMP SHIFT

· 1 cycle DRAM read or write (pipelined)

· Glue-less memory- and I/O-connection

· 80 mW @ 50 MHz power dissipation

· Fully automatic power-down mode

· Clock-off function

· Operating Voltage: 2.4V...5V

Compact architecture and high performance give

you a solid base for meeting or exceeding your

project requirements Hyperstone E1-32X/E1-16X

RISC/DSP

Compact design and low power consumption.

The Hyperstone's minimum transistor count results in

a low power consumption of about 80 mW at 50 MHz

(2.7 V) for the complete chip. An automatic power-

down reduces power consumption even further in

many applications. Due to the on-chip bus interface,

total power consumption depends on the external

load connected to the chip. The low power consumption

makes very small packages possible.

Various Types

The Hyperstone E1-32X RISC/DSP family is available

in various types. The external data bus-width is 32 bit

and 16 bit for the E1-32X and E1-16 series, respectively.

The package types for the E1-32X series are 144-pin

TQFP (20 x 20 x 1.4mm) and 160-pin PQFP

(28 x 28 x 3.4mm), whereas the E1-16X series comes

in a very compact (14 x 14 x 1.4mm) 100-pin TQFP

package. Each type has 8 kByte on-chip RAM and

maximum clock rates of up to 80 MHz.

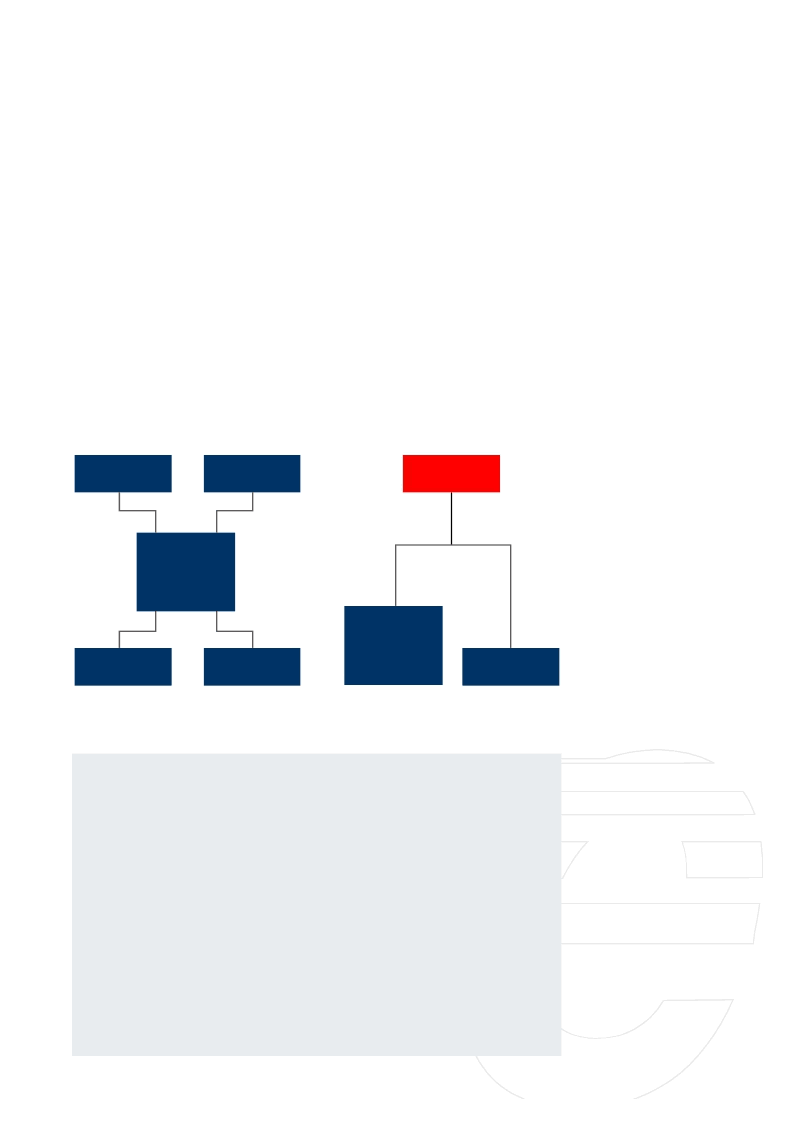

Hyperstone

RISC/DSP

CPU

DSP

Memory

Peripherals

Glue logic

decoders

latches

memory control

I/O control etc.

Memory

DRAM

EDO RAM

(Flash-)EPROM

SRAM

Peripherals

no glue logic

Hyperstone Architecture

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RIVA 128ZX | 128-Bit 3D Multimedia Accelerator(128位3D多媒體加速器) |

| RIVA128ZX | 128-BIT 3D MULTIMEDIA ACCELERATOR |

| RIVA128 | RIVA 128⑩ 128-BIT 3D MULTIMEDIA ACCELERATOR |

| RIX-0142-H | FILTER IEC EINGANG ULTRA KOMPAKT 1A |

| RIX-0342-H | FILTER IEC EINGANG ULTRA KOMPAKT 3A |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RISC806960D | 制造商:RFPD COMPONENT SOLUTIONS 功能描述:CIRCULATOR/ISOLATOR |

| RISC806960S | 制造商:RFPD COMPONENT SOLUTIONS 功能描述:CIRCULATOR/ISOLATOR |

| RI-SMD-MRD2 | 制造商:Texas Instruments 功能描述:HDX MICROREADER SMD 制造商:Texas Instruments 功能描述:HDX MICROREADER SMD - Boxed Product (Development Kits) |

| R-IS-N-F | 制造商:LAB FACILITY 功能描述:TYPE N STDRD T-COUPLE |

| R-IS-N-M | 制造商:LAB FACILITY 功能描述:TYPE N STDRD T-COUPLE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。