- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374571 > RC4200 (Fairchild Semiconductor Corporation) Analog Multiplier PDF資料下載

參數(shù)資料

| 型號(hào): | RC4200 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Analog Multiplier |

| 中文描述: | 模擬乘法器 |

| 文件頁數(shù): | 2/23頁 |

| 文件大小: | 206K |

| 代理商: | RC4200 |

RC4200

PRODUCT SPECIFICATION

2

REV. 1.2.1 6/14/01

Functional Description

The RC4200 multiplier is designed to multiply two input

currents (I

1

and I

2

) and to divide by a third input current (I

4

).

The output is also in the form of a current (I

3

). A simplified

circuit diagram is shown in the Block Diagram. The nominal

relationship between the three inputs and the output is:

The three input currents must be positive and restricted to a

range of 1 μA to 1 mA. These currents go into the multiplier

chip at op amp summing junctions which are nominally at

zero volts. Therefore, an input voltage can be easily

converted to an input current by a series resistor. Any

number of currents may be summed at the inputs. Depending

on the application, the output current can be converted to a

voltage by an external op amp or used directly. This capa-

bilty of combining input currents and voltages in various

combinations provides great versatility in application.

Inside the multiplier chip, the three op amps make the

collector currents of transistors Q1, Q2 and Q4 equal to their

respective input currents (I

1

, I

2

, and I

4

). These op amps are

designed with current source outputs and are phase-compen-

sated for optimum frequency response as a multiplier. Power

drain of the op amps was minimized to prevent the introduc-

tion of undesired thermal gradients on the chip. The three op

amps operate on a single supply voltage (nominally -15V)

and total quiescent current drain is less than 4 mA. These

special op amps provide significantly improved performance

in comparison to 741-type op amps.

The actual multiplication is done within the log-antilog

configuration of the Q1-Q4 transistor array. These four

transistors, with associated proprietary circuitry, were

specially designed to precisely implement the relationship.

I

3

I

I

I

4

--------- 1

=

V

BEN

kT

Q

------InI

I

SN

-------- 2

=

Previous multiplier designs have suffered from an additional

undesired linear term in the above equation; the collector

current times the emitter resistance. The I

C

r

E

term intro-

duces a parabolic nonlinearity even with matched transistors.

Fairchild Semiconductor has developed a unique and propri-

etary means of inherently compensating for this undesired

I

C

r

E

term. Furthermore, this Fairchild Semiconductor devel-

oped circuit technique compensates linearity error over tem-

perature changes. The nonlinearity versus temperature is

significantly improved over earlier designs.

From equation (2) and by assuming equal transistor junction

temperatures, summing base-to-emitter voltage drops around

the transistor array yields:

This equation reduces to:

The rate of reverse saturation current I

S1

I

S2

/I

S3

I

S4

, depends

on the transistor matching. In a monolithic multiplier this

matching is easily achieved and the rate is very close to

unity, typically 1.0±1%. The final result is the desired

relationship:

The inherent linearity and gain stability combined with low

cost and versatility makes this new circuit ideal for a wide

range of nonlinear functions.

q

KT

I

1

I

S1

-------

In

I

2

I

S2

-------

In

I

I

S3

-------–

I

4

I

S4

-------

–

=

0 3

=

I

I

2

I

3

I

4

---------

I

I

I

S3

I

S4

--------------- 4

=

I

3

I

I

I

4

--------- 5

=

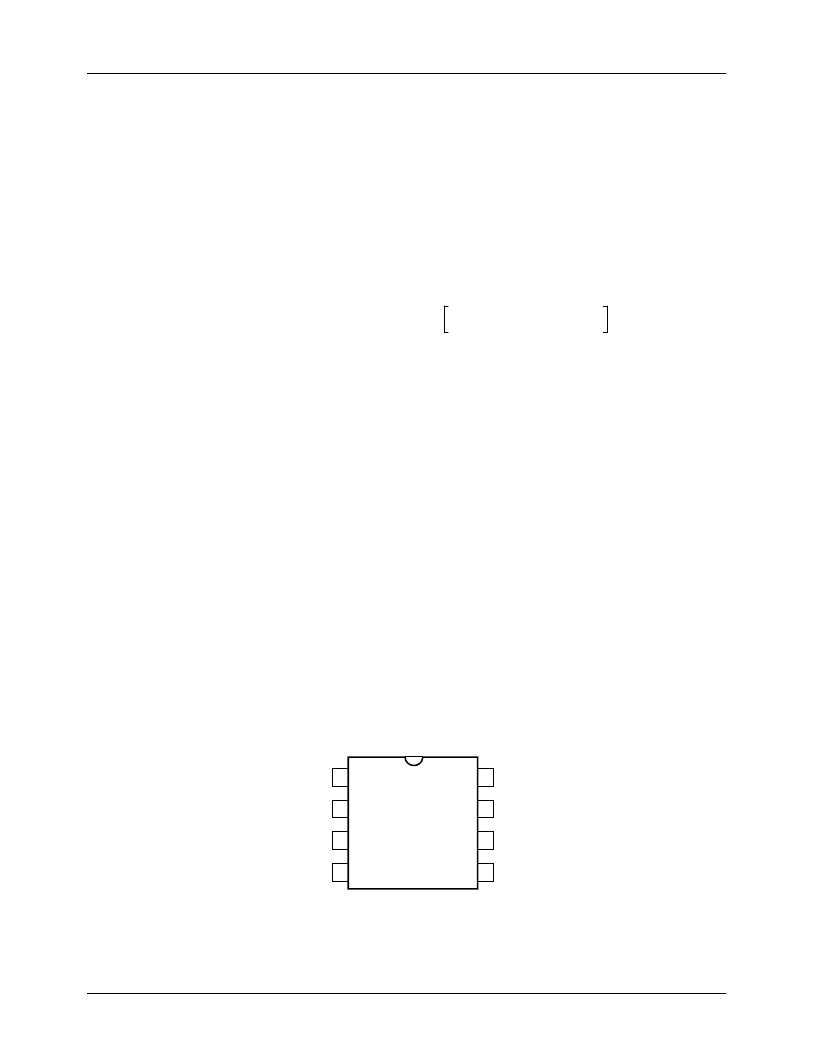

Pin Assignments

1

2

3

4

I2

VOS2

–

VS

I3 (Output)

I1

VOS1

GND

I4

8

7

6

5

65-4200-07

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RC431A | Low-Voltage Adjustable Precision Shunt Regulator |

| RC0431 | Low-Voltage Adjustable Precision Shunt Regulator |

| RC0431A | Low-Voltage Adjustable Precision Shunt Regulator |

| RC4391 | Inverting and Step-Down Switching Regulator |

| RC4391M | Inverting and Step-Down Switching Regulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RC4200AM | 功能描述:增效器/分頻器 SOIC-8 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| RC4200AMT | 功能描述:增效器/分頻器 SOIC-8 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| RC4200AMT_32 | 功能描述:增效器/分頻器 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| RC4200AN | 功能描述:增效器/分頻器 DIP-8 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| RC4200AN_32 | 功能描述:增效器/分頻器 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。