- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361292 > QL5064-33APB484C BUS CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | QL5064-33APB484C |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 總線控制器 |

| 文件頁數(shù): | 22/37頁 |

| 文件大小: | 806K |

| 代理商: | QL5064-33APB484C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

QL5064 QuickPCI Data Sheet

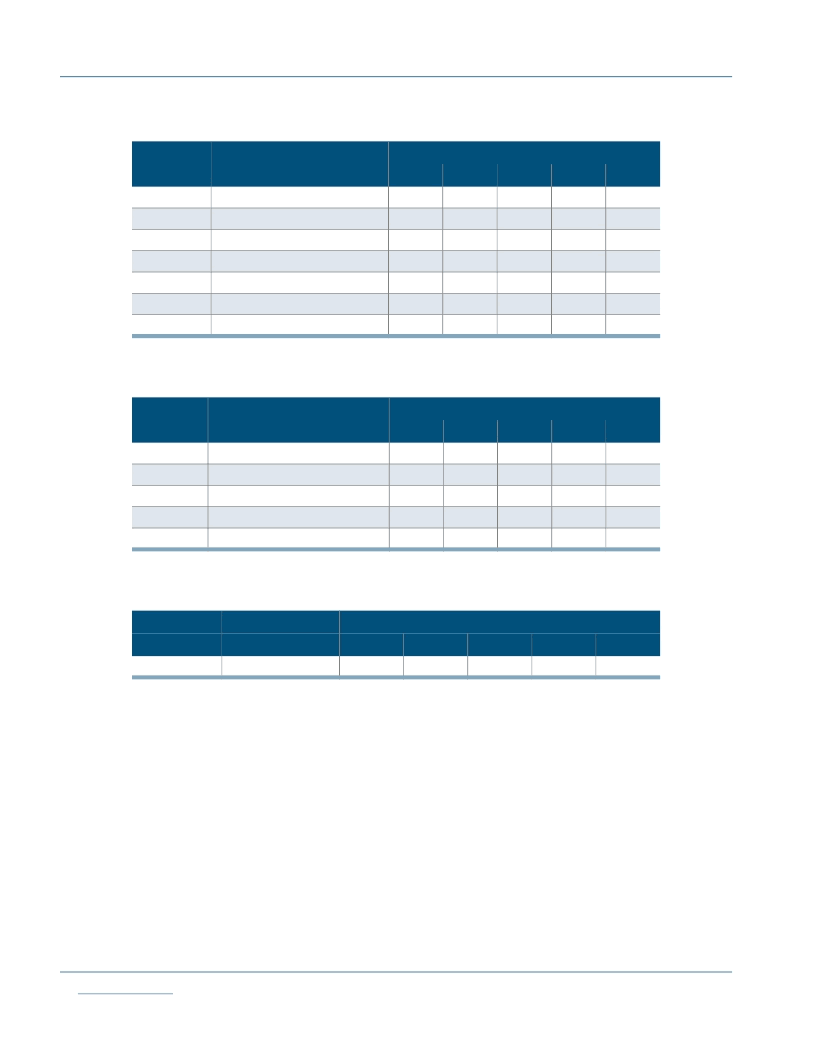

Table 3: RAM Cell Synchronous Write Timing

Symbol

Parameter

Propagation Delays (ns)Fanout

1

2

3

4

8

TSWA

WA Setup Time to WCLK

1.0

1.0

1.0

1.0

1.0

THWA

WA Hold Time to WCLK

0.0

0.0

0.0

0.0

0.0

TSWD

WD Setup Time to WCLK

1.0

1.0

1.0

1.0

1.0

THWD

WD Hold Time to WCLK

0.0

0.0

0.0

0.0

0.0

TSWE

WE Setup Time to WCLK

1.0

1.0

1.0

1.0

1.0

THWE

WE Hold Time to WCLK

0.0

0.0

0.0

0.0

0.0

TWCRD

WCLK to RD (WA=RA) [a]

5.0

5.3

5.6

5.9

7.1

Table 4: RAM Cell Synchronous Read Timing

Symbol

Parameter

Propagation Delays (ns)Fanout

a

1

2

3

4

8

TSRA

RA Setup Time to RCLK

1.0

1.0

1.0

1.0

1.0

THRA

RA Hold Time to RCLK

0.0

0.0

0.0

0.0

0.0

TSRE

RE Setup Time to RCLK

1.0

1.0

1.0

1.0

1.0

THRE

RE Hold Time to RCLK

0.0

0.0

0.0

0.0

0.0

TRCRD

RCLK to RD [b]

4.0

4.3

4.6

4.9

6.1

Table 5: RAM Cell Asynchronous Read T iming

Symbol

Parameter

Propagation Delays (ns)Fanout

1

2

3

4

8

RPDRD

RA to RD [b]

3.0

3.3

3.6

3.9

5.1

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。