- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄224944 > PWR-82330-490Q Industrial Control IC PDF資料下載

參數(shù)資料

| 型號(hào): | PWR-82330-490Q |

| 英文描述: | Industrial Control IC |

| 中文描述: | 工業(yè)控制IC |

| 文件頁(yè)數(shù): | 8/12頁(yè) |

| 文件大小: | 361K |

| 代理商: | PWR-82330-490Q |

5

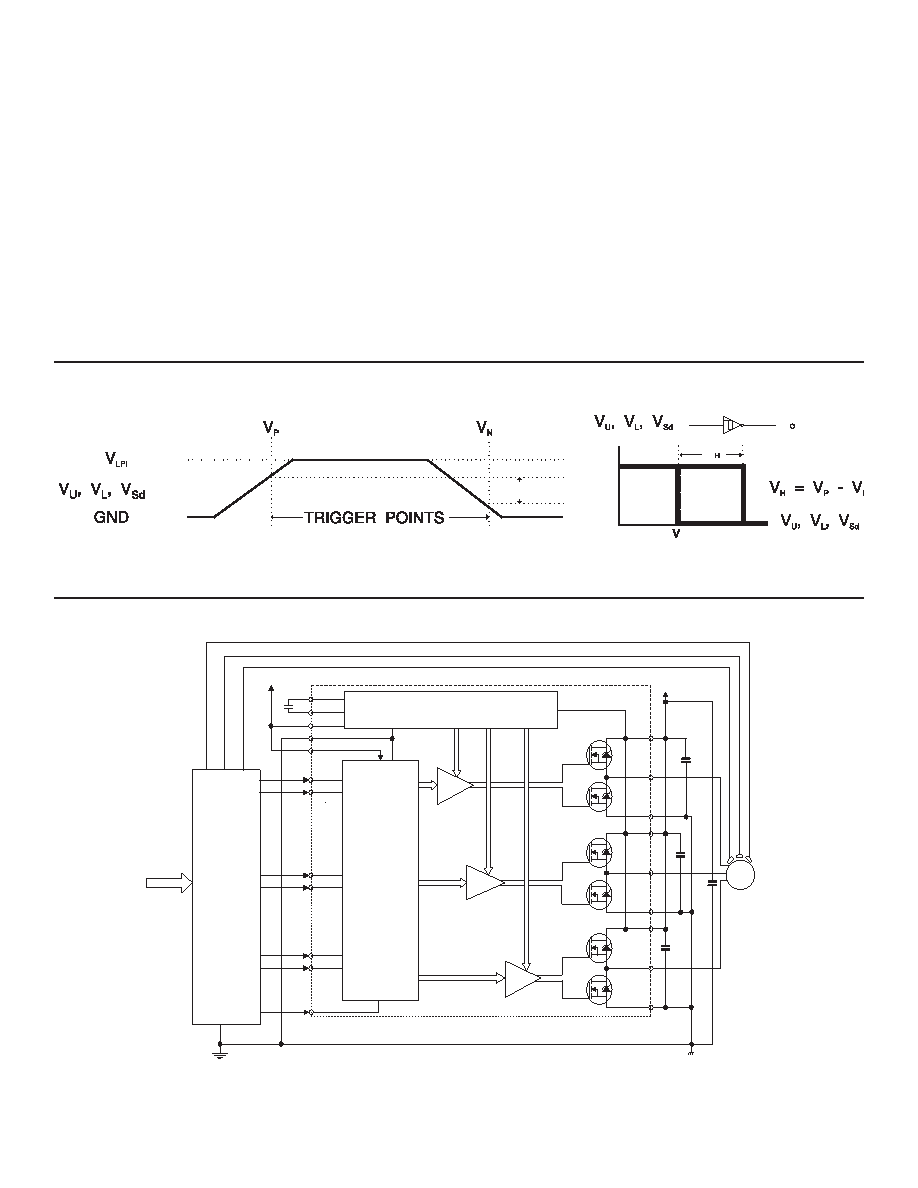

FIGURE 4. TYPICAL INTERFACE WITH A MOTOR AND COMMUTATION LOGIC

+28V

CHARGE PUMP

+15V

+CAP

VUA

VLPI

VLA

-CAP

V+

GND

DRIVE

A

VCC A

VO A

TANT +

MOTOR

HALL

EFFECT

DEVICES

V

VCC B

VO B

VSS B

SS A

B

DIGITAL

CONTROL

AND

PROTECTION

CIRCUITRY

DRIVE

VUB

VLB

POSITION

LOOP

AND

COMMUTATION

LOGIC

POSITION

COMMAND

VUC

VLC

DRIVE

C

VCC C

VO C

VSS C

PWR-82330

VSd

+

FIGURE 3. HYSTERESIS DEFINITION AND CHARACTERISTICS

SHUT-DOWN INPUT (VSd)

Pin 12 (Vsd) provides a digital shut-down input, which allows the

user to completely turn-off both the upper and lower-output tran-

sistors in all 3 phases. Application of a logic ‘1’ to the VSd input

will latch the Digital Control / Protection circuitry thereby turning

off all output transistors. The Digital Control/Protection circuitry

remains latched in the off state and will not respond to signals on

the VL or VU inputs while the VSd has a logic ‘1’ applied. When

the user or the sense circuitry (as in FIGURE 6) returns the VSd

input to a logic ‘0’, and then the user sets the VL and VU inputs

to a logic ‘0’ the output of the Digital Control / Protection circuit-

ry will clear the internal latch. When the next rising edge (see

L or VU digital inputs, the outputs

transistors will respond to the corresponding digital input. This

feature can be used with external current limit or temperature

sense circuitry to disable the drive if a fault condition occurs (see

FIGURE 6).

INTERNAL PROTECTION CIRCUITRY

The hybrid contains digital protection circuitry, which prevents in-

line transistors from conducting simultaneously. This, in effect,

would short circuit the power supply and would damage the out-

put stage of the hybrid. The circuitry allows only proper input sig-

nal patterns to cause output conduction. TABLE 3 lists the input/

output timing relationships. If an improper input requested that

the upper and lower transistors of the same phase conduct

together, the output would be a high impedance until removal of

the illegal code from the input of the PWR-82330. A dead time

of 400 nsec minimum should still be maintained between

1

2

V

v

VO

V

H

vp

N

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PWR-82330-490S | Industrial Control IC |

| PWR-82330-490W | Industrial Control IC |

| PWR-82330-490Y | Industrial Control IC |

| PWR-82330-490Z | Industrial Control IC |

| PWR-82330-500 | Industrial Control IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PWR-82330-490S | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

| PWR-82330-490W | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

| PWR-82330-490Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

| PWR-82330-490Z | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

| PWR-82330-500 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。