采購(gòu)需求

(若只采購(gòu)一條型號(hào),填寫(xiě)一行即可)| *型號(hào) | *數(shù)量 | 廠商 | 批號(hào) | 封裝 |

|---|---|---|---|---|

|

|

添加更多采購(gòu)

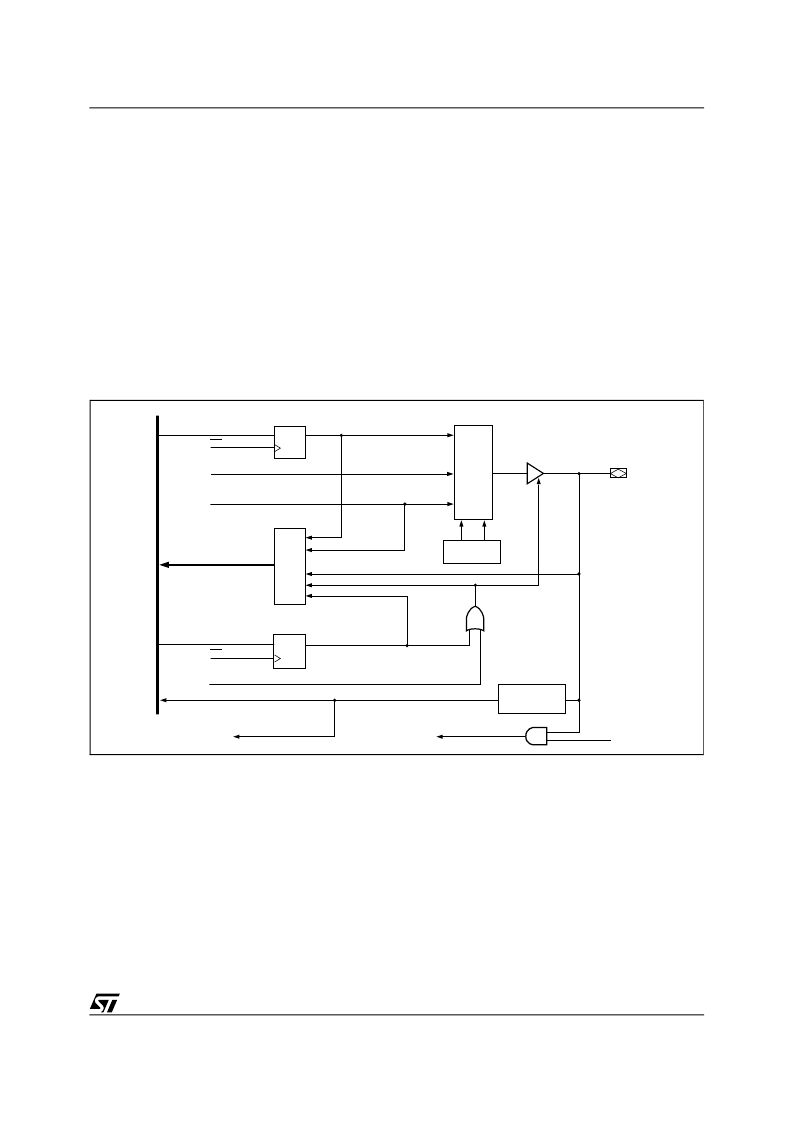

| 型號(hào): | PSD853490JIT |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| 中文描述: | Flash在系統(tǒng)可編程ISP的外設(shè)的8位微控制器 |

| 文件頁(yè)數(shù): | 59/110頁(yè) |

| 文件大?。?/td> | 1737K |

| 代理商: | PSD853490JIT |

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD853490JT | 120V Boot, 3-A Peak, High Frequency, High-Side/Low-Side Driver 8-SOIC -40 to 125 |

| PSD853490MIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD853490MT | 120V Boot, 3-A Peak, High Frequency, High-Side/Low-Side Driver 8-VSON -40 to 125 |

| PSD8534V15JT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD8534V15MT | 120V Boot, 3-A Peak, High Frequency, High-Side/Low-Side Driver 8-VSON -40 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD853F2-70J | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 5.0V 1M 70ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD853F2-70M | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 1M 70ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD853F2-90J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD853F2-90JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD853F2-90M | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| *型號(hào) | *數(shù)量 | 廠商 | 批號(hào) | 封裝 |

|---|---|---|---|---|

|

|