- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368227 > PSD4235G2-B-70JI (意法半導(dǎo)體) Solid Tantalum Chip Capacitors / T491 Series - Precision Molded Chip; Capacitance [nom]: 0.47uF; Working Voltage (Vdc)[max]: 35V; Capacitance Tolerance: +/-10%; Dielectric: Tantalum, Solid; Lead Style: Surface-Mount Chip; Lead Dimensions: 3216-18; Termination: 100% Tin (Sn); Body Dimensions: 3.2mm x 1.6mm x 1.6mm; Temperature Range: -55C to +125C; Container: Tape & Reel; Qty per Container: 2,000 PDF資料下載

參數(shù)資料

| 型號(hào): | PSD4235G2-B-70JI |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Solid Tantalum Chip Capacitors / T491 Series - Precision Molded Chip; Capacitance [nom]: 0.47uF; Working Voltage (Vdc)[max]: 35V; Capacitance Tolerance: +/-10%; Dielectric: Tantalum, Solid; Lead Style: Surface-Mount Chip; Lead Dimensions: 3216-18; Termination: 100% Tin (Sn); Body Dimensions: 3.2mm x 1.6mm x 1.6mm; Temperature Range: -55C to +125C; Container: Tape & Reel; Qty per Container: 2,000 |

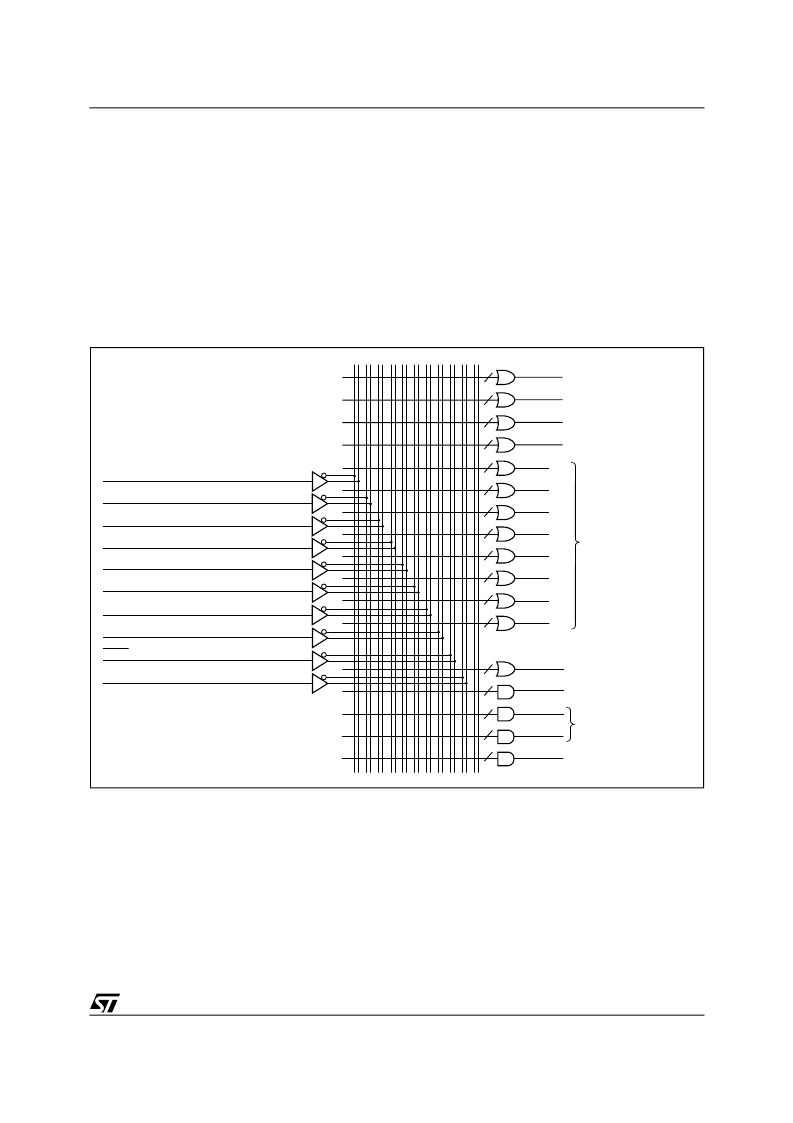

| 中文描述: | Flash在系統(tǒng)可編程外設(shè)的16位微控制器 |

| 文件頁(yè)數(shù): | 33/89頁(yè) |

| 文件大小: | 703K |

| 代理商: | PSD4235G2-B-70JI |