- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382383 > PCM1717E Stereo Audio DIGITAL-TO-ANALOG CONVERTER PDF資料下載

參數(shù)資料

| 型號(hào): | PCM1717E |

| 英文描述: | Stereo Audio DIGITAL-TO-ANALOG CONVERTER |

| 中文描述: | 立體聲音頻數(shù)字模擬轉(zhuǎn)換器 |

| 文件頁(yè)數(shù): | 14/14頁(yè) |

| 文件大小: | 126K |

| 代理商: | PCM1717E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)

14

PCM1717

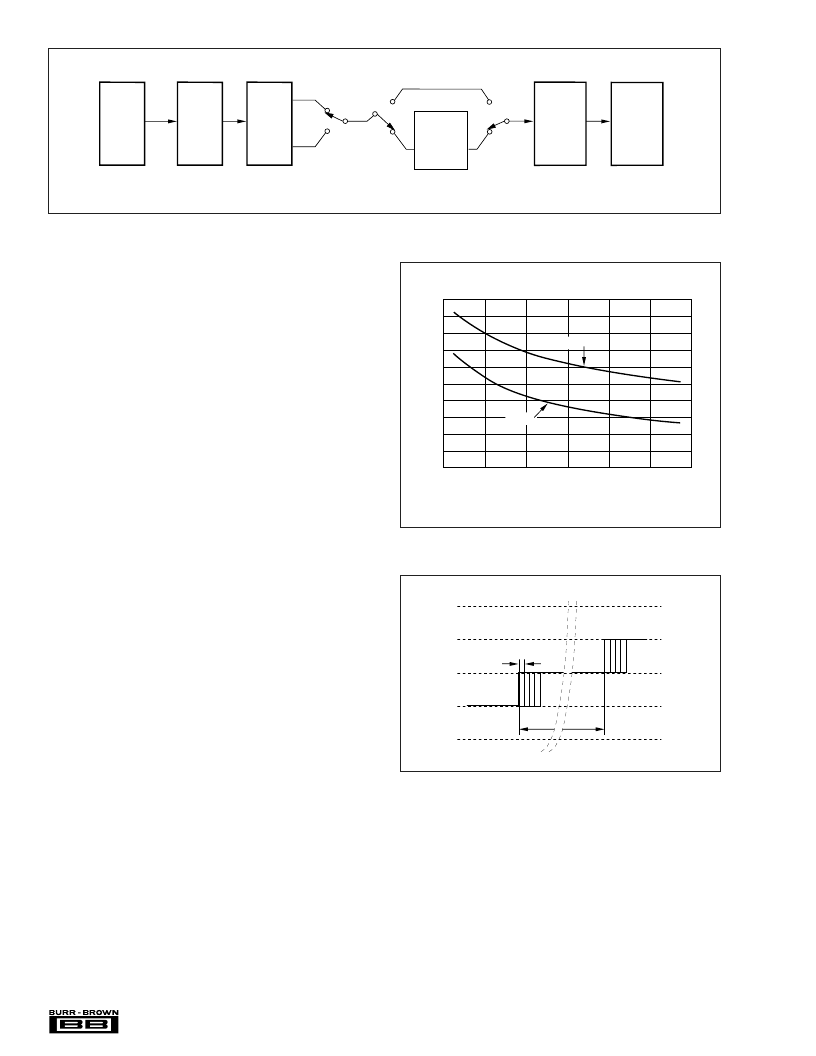

FIGURE 17. Test Block Diagram.

PGA

Digital

Lch

Rch

DEM-

PCM1717

CD

Player

DAI

11th-order

LPF

THD

Meter

0dB/60dB

30KHz LPF on

Through

For test of S/N ratio and Dynamic Range, A-filter ON.

Test Disk

Shibasoku #725

0

100

200

300

400

500

600

110

105

100

95

90

85

80

75

70

65

60

D

Clock Jitter (ps)

Multi-level

PWM

FIGURE 18. Simulation Results of Clock Jitter Sensitivity.

FIGURE 19. Simulation Method for Clock Jitter.

2

1

0

–1

2

48fs

14.4ps

TEST CONDITIONS

Figure 17 illustrates the actual test conditions applied to

PCM1717 in production. The 11th-order filter is necessary

in the production environment for the removal of noise

resulting from the relatively long physical distance between

the unit and the test analyzer. In most actual applications, the

3rd-order filter shown in Figure 16 is adequate. Under

normal conditions, THD+N typical performance is –70dB

with a 30kHz low pass filter (shown here on the THD

meter), improving to –89dB when the external 20kHz 11th-

order filter is used.

EVALUATION FIXTURES

Three evaluation fixtures are available for PCM1717.

DEM-PCM1717

This evaluation fixture is primarily intended for quick evalu-

ation of the PCM1717’s performance. DEM-PCM1717 can

accept either an external clock or a user-installed crystal

oscillator. All of the functions can be controlled by on-board

switches. DEM-PCM1717 does not contain a receiver chip

or an external low pass filter. DEM-PCM1717 requires a

single +5V power supply.

OUT-OF-BAND NOISE CONSIDERATIONS

Delta-sigma DACs are by nature very sensitive to jitter on

the master clock. Phase noise on the clock will result in an

increase in noise, ultimately degrading dynamic range. It is

difficult to quantify the effect of jitter due to problems in

synthesizing low levels of jitter. One of the reasons delta-

sigma DACs are prone to jitter sensitivity is the large

quantization noise when the modulator can only achieve two

discrete output levels (0 or 1). The multi-level delta-sigma

DAC has improved theoretical SNR because of multiple

output states. This reduces sensitivity to jitter. Figure 18

contrasts jitter sensitivity between a one-bit PWM type DAC

and multi-level delta-sigma DAC. The data was derived

using a simulator, where clock jitter could be completely

synthesized.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCM1718 | Stereo Audio DIGITAL-TO-ANALOG CONVERTER |

| PCM1718E | Stereo Audio DIGITAL-TO-ANALOG CONVERTER |

| PCM1719 | Stereo Audio DIGITAL-TO-ANALOG CONVERTER |

| PCM1719E | Stereo Audio DIGITAL-TO-ANALOG CONVERTER |

| PCM1720 | Stereo Audio DIGITAL-TO-ANALOG CONVERTER MPEG2/AC-3 COMPATIBLE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCM1717E/2K | 功能描述:音頻數(shù)/模轉(zhuǎn)換器 IC SoundPlus Stereo DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量: 分辨率:16 bit 接口類型:I2S, UBS 轉(zhuǎn)換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數(shù)量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| PCM1717E/2KG4 | 功能描述:音頻數(shù)/模轉(zhuǎn)換器 IC SoundPlus Stereo DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量: 分辨率:16 bit 接口類型:I2S, UBS 轉(zhuǎn)換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數(shù)量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| PCM1717EG | 功能描述:音頻數(shù)/模轉(zhuǎn)換器 IC SoundPlus Stereo DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量: 分辨率:16 bit 接口類型:I2S, UBS 轉(zhuǎn)換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數(shù)量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| PCM1717EG4 | 功能描述:音頻數(shù)/模轉(zhuǎn)換器 IC SoundPlus Stereo DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量: 分辨率:16 bit 接口類型:I2S, UBS 轉(zhuǎn)換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數(shù)量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| PCM1717EGE6 | 功能描述:音頻數(shù)/模轉(zhuǎn)換器 IC SoundPlus Stereo DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量: 分辨率:16 bit 接口類型:I2S, UBS 轉(zhuǎn)換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數(shù)量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。