- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382382 > PCF8575 (NXP Semiconductors N.V.) Remote 16-bit I/O expander for I2C-bus PDF資料下載

參數(shù)資料

| 型號: | PCF8575 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Remote 16-bit I/O expander for I2C-bus |

| 中文描述: | 遠程16位I / O擴展I2C總線 |

| 文件頁數(shù): | 6/24頁 |

| 文件大小: | 105K |

| 代理商: | PCF8575 |

1999 Apr 07

6

Philips Semiconductors

Product specification

Remote 16-bit I/O expander for I

2

C-bus

PCF8575

6

CHARACTERISTICS OF THE I

2

C-BUS

The I

2

C-bus is for bidirectional, 2-line communication

between different ICs or modules. The two lines are a

serial data line (SDA) and a serial clock line (SCL). Both

lines must be connected to a positive supply via a pull-up

resistor when connected to the output stages of a device.

Data transfer may be initiated only when the bus is not

busy.

6.1

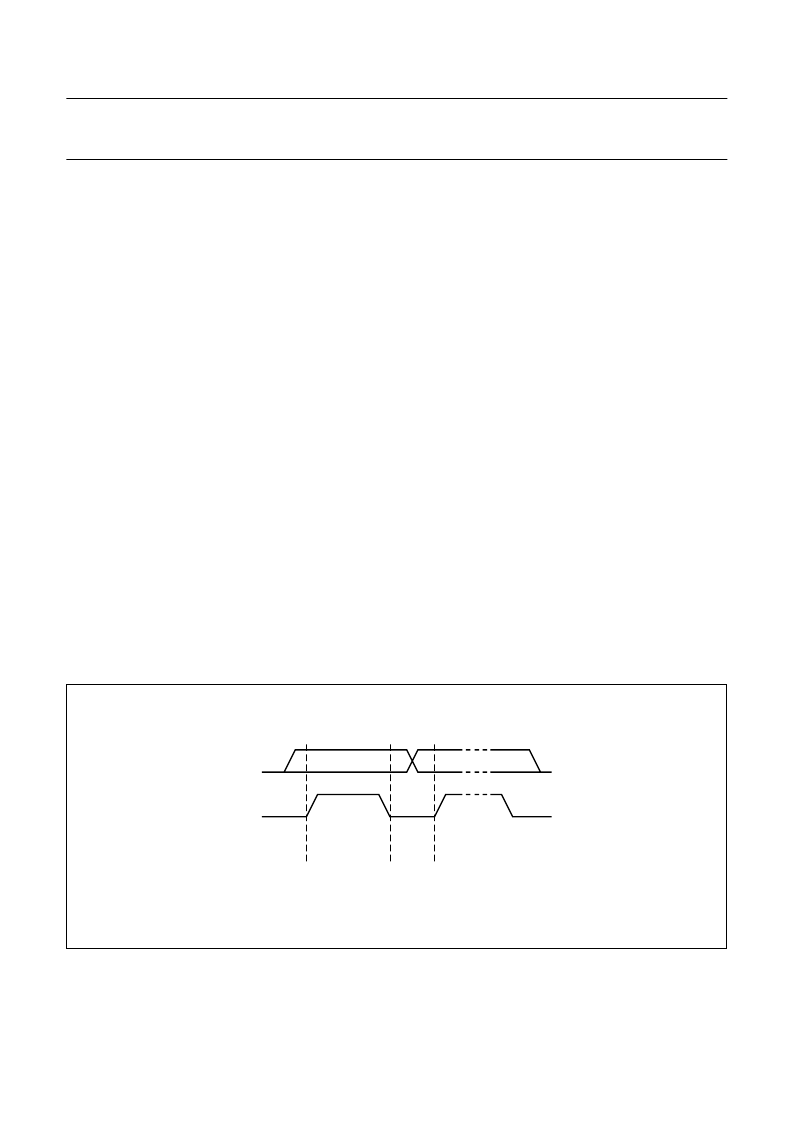

Bit transfer

One data bit is transferred during each clock pulse.

The data on the SDA line must remain stable during the

HIGH period of the clock pulse as changes in the data line

at this time will be interpreted as control signals

(see Fig.3).

6.2

START and STOP conditions

Both data and clock lines remain HIGH when the bus is not

busy. A HIGH-to-LOW transition of the data line, while the

clock is HIGH is defined as the START condition (S).

A LOW-to-HIGH transition of the data line while the clock

is HIGH is defined as the STOP condition P (see Fig.4).

6.3

System configuration

A device generating a message is a ‘transmitter’, a device

receiving the message is the ‘receiver’. The device that

controls the message is the ‘master’ and the devices which

are controlled by the master are the ‘slaves’ (see Fig.5).

6.4

Acknowledge

The number of data bytes transferred between the START

and the STOP conditions from transmitter to receiver is not

limited. Each byte of eight bits is followed by one

acknowledge bit. The transmitter must release the SDA

line before the receiver can send an acknowledge bit.

A slave receiver which is addressed must generate an

acknowledge after the reception of each byte. Also a

master must generate an acknowledge after the reception

of each byte that has been clocked out of the slave

transmitter. The device that acknowledges has to pull

down the SDA line during the acknowledge clock pulse, so

that the SDA line is stable LOW during the HIGH period of

the acknowledge related clock pulse, set-up and hold

times must be taken into account.

A master receiver must signal an end of data to the

transmitter by

not

generating an acknowledge after the

last byte that has been clocked out of the slave. This is

done by the master receiver by holding the SDA line HIGH.

In this event the transmitter must release the data line to

enable the master to generate a STOP condition.

Fig.3 Bit transfer.

handbook, full pagewidth

MBC621

data line

stable;

data valid

change

of data

allowed

SDA

SCL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF8576 | Universal LCD driver for low multiplex rates |

| PCF8576C | Universal LCD driver for low multiplex rates |

| PCF8576CH | Universal LCD driver for low multiplex rates |

| PCF8576U | Universal LCD driver for low multiplex rates |

| PCF8577C | LCD direct/duplex driver with I2C-bus interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF8575C | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Remote 16-bit I/O expander for I2C-bus |

| PCF8575CDB | 功能描述:接口-I/O擴展器 Remote 16-Bit I2C & SMBus I/O Expander RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| PCF8575CDBE4 | 功能描述:接口-I/O擴展器 Remote 16-Bit I2C & SMBus I/O Expander RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| PCF8575CDBG4 | 功能描述:接口-I/O擴展器 Rem 16B I2C & SMBus I/O Expander RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| PCF8575CDBQR | 功能描述:接口-I/O擴展器 Remote 16-Bit I2C & SMBus I/O Expander RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。