- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD3359AP (NXP SEMICONDUCTORS) 8-bit microcontroller with DTMF generator and 128 bytes EEPROM PDF資料下載

參數(shù)資料

| 型號: | PCD3359AP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-bit microcontroller with DTMF generator and 128 bytes EEPROM |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP28 |

| 封裝: | 0.600 INCH, PLASTIC, DIP-28 |

| 文件頁數(shù): | 14/32頁 |

| 文件大小: | 165K |

| 代理商: | PCD3359AP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

1998 May 11

14

Philips Semiconductors

Product specification

8-bit microcontroller with DTMF

generator and 128 bytes EEPROM

PCD3359A

7.1.2

EEPROM A

DDRESS

R

EGISTER

(ADDR)

The EEPROM Address Register determines the EEPROM location to which an EEPROM access is directed.

As a whole, ADDR auto-increments after read and write cycles to EEPROM, but remains fixed after erase cycles. This

behaviour generates the correct ADDR contents for sequential read accesses and for sequential write or erase/write

accesses with intermediate page setup. Overflow of the 8-bit counter wraps around to zero.

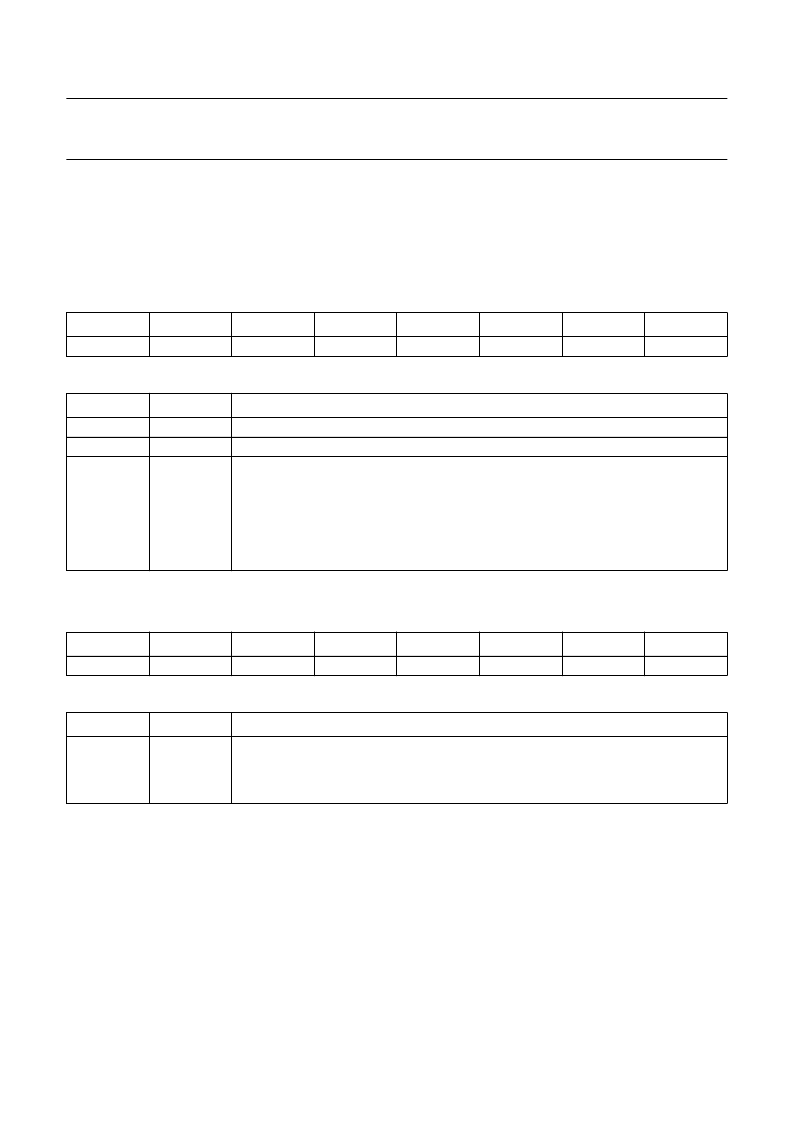

Table 14

EEPROM Address Register, ADDR (address 01H, access type R/W)

Table 15

Description of ADDR bits

7.1.3

EEPROM D

ATA

R

EGISTER

(DATR)

Table 16

EEPROM Data Register (address 03H; access type R/W)

Table 17

Description of DATR bits

7.1.4

EEPROM T

EST

R

EGISTER

(TST)

The EEPROM Test Register is used for testing purposes during device manufacture. It must not be accessed by the

device user.

7.2

EEPROM latches

The four EEPROM latches (EEPROM Latch 0 to 3; Fig.5) cannot be read by user software. Due to their construction, the

latches can only be preset, but not cleared. Successive write operations through DATR to the EEPROM latches actually

perform a logical OR with the previously stored data in EEPROM. The EEPROM latches are reset at the conclusion of

any EEPROM cycle.

7

6

5

4

3

2

1

0

0

AD6

AD5

AD4

AD3

AD2

AD1

AD0

BIT

SYMBOL

AD6 to AD2

AD1 to AD0

DESCRIPTION

7

This bit is set to a logic 0.

AD2 to AD6 select one of 32 pages.

AD1 and AD0 are irrelevant during erase and write cycles. For read accesses, AD0 and

AD1 indicate the byte location within an EEPROM page. During page setup, finally, AD0

and AD1 select EEPROM Latch 0 to 3 whereas AD2 to AD6 are irrelevant. If increment

mode (Table 13) is active during page setup, the subcounter consisting of AD0 and AD1

increments after every write to an EEPROM latch, thus enhancing access to sequential

EEPROM latches. Incrementing stops when EEPROM Latch 3 is reached, i.e. when

AD0 and AD1 are both a logic 1.

6 to 2

1 to 0

7

6

5

4

3

2

1

0

D7

D6

D5

D4

D3

D2

D1

D0

BIT

SYMBOL

DESCRIPTION

7 to 0

D7 to D0

The EEPROM Data Register (DATR) is only a conceptual entity. A read operation from

DATR, reads out the EEPROM byte addressed by ADDR. On the other hand, a write

operation to DATR, loads data into the EEPROM latch (see Fig.5) defined by bits AD0

and AD1 of ADDR.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD3359AT | 8-bit microcontroller with DTMF generator and 128 bytes EEPROM |

| PCD3360 | Programmable multi-tone telephone ringer |

| PCD3360P | Programmable multi-tone telephone ringer |

| PCD3360T | Programmable multi-tone telephone ringer |

| PCD4440T | Analog voice scrambler/descrambler |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD3359AT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with DTMF generator and 128 bytes EEPROM |

| PCD3360 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Programmable multi-tone telephone ringer |

| PCD3360P | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Programmable multi-tone telephone ringer |

| PCD3360T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Programmable multi-tone telephone ringer |

| PCD33XXA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-Bit telecom microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。