- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369949 > PCB2421P (NXP SEMICONDUCTORS) 1K dual mode serial EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | PCB2421P |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | PROM |

| 英文描述: | 1K dual mode serial EEPROM |

| 中文描述: | I2C/2-WIRE SERIAL EEPROM, PDIP8 |

| 封裝: | 0.300 MIL, PLASTIC, MO-001-AN, SOT-97-1, DIP-8 |

| 文件頁(yè)數(shù): | 7/24頁(yè) |

| 文件大小: | 112K |

| 代理商: | PCB2421P |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

1997 Apr 01

7

Philips Semiconductors

Preliminary specification

1K dual mode serial EEPROM

PCB2421

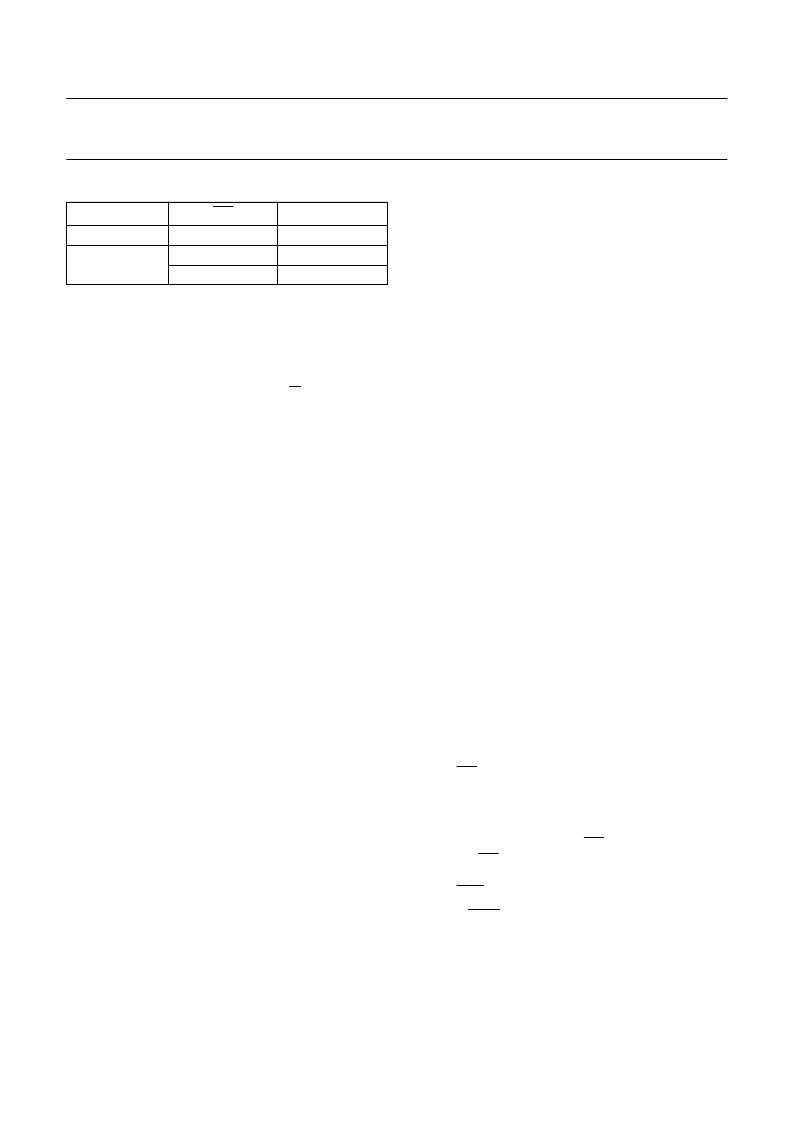

Table 2

Mode configurations

Note

1.

Where X = don’t care.

6.7

Read operation

Read operations are initiated in the same way as write

operations with the exception that the R/W bit of the slave

address is set to logic 1. There are three basic types of

read operations: current address read, random read, and

sequential read.

6.7.1

C

URRENT ADDRESS READ

The PCB2421 contains an address counter that maintains

the address of the last word accessed, internally

incremented by one. Therefore, if the previous access

(either a read or write operation) was to address ‘n’, the

next current address read operation would access data

from address n + 1. Upon receipt of the slave address with

R/W set to logic 1, the PCB2421 issues an acknowledge

and transmits the eight bit data word. The master will not

acknowledge the transfer but does generate a STOP

condition and the PCB2421 discontinues transmission

(see Fig.10).

6.7.2

R

ANDOM READ

Random read operations allow the master to access any

memory location in a random manner. To perform this type

of read operation, the word address must first be set. This

is done by sending the word address to the PCB2421 as

part of a normal write operation. After the word address is

sent, the master generates a REPEATED START

condition following the acknowledge. This terminates the

write operation, but not before the internal address pointer

is set. The master then issues the control byte again but

with the R/W bit set to logic 1. The PCB2421 will then issue

an acknowledge and transmits the 8-bit data word.

The master will not acknowledge the transfer but does

generate a STOP condition and the PCB2421

discontinues transmission (see Fig.11).

6.7.3

S

EQUENTIAL READ

Sequential reads are initiated in the same way as a

random read except that after the PCB2421 transmits the

first data byte, the master issues an acknowledge as

DDC

WP

X

(1)

1

0

MODE

DCC1

DCC2

R

R/W

R

opposed to a STOP condition in a random read.

This directs the PCB2421 to transmit the next sequentially

addressed 8-bit word. To provide sequential reads the

PCB2421 contains an internal address pointer which is

incremented by one at the completion of each operation.

This address pointer allows the entire memory contents to

be serially read during one operation.

6.8

Pin description

6.8.1

SDA

This pin is used to transfer addresses and data into and

out of the device, when the device is in the bidirectional

(I

2

C-bus, DDC2B) mode. In the transmit-only mode

(DDC1), which only allows data to be read from the device,

data is also transferred on the SDA pin. This pin is an

open-drain terminal, therefore the SDA bus requires a

pull-up resistor connected to V

DD

(typically 10 k

for

100 kHz). See brochure “The I

2

C-bus and how to use it”

(order no. 9398 393 40011) or “Data Handbook IC12”

6.8.2

SCL

This pin is the clock input for the bidirectional mode

(I

2

C-bus, DDC2B), and is used to synchronize data

transfer to and from the device. It is also used as the

signalling input to switch the device from the transmit-only

mode to the bidirectional mode. It must remain HIGH for

the chip to continue operation in the transmit-only mode

(DDC1).

6.8.3

VCLK

This pin is the clock input for the transmit-only mode

(DDC1). In the transmit-only mode, each bit is clocked out

on the rising edge of this signal. In DDC2B mode, this input

is a don’t care.

6.8.4

WP

This pin is used to inhibit writing of the EEPROM. When

this pin is connected to ground, writing of the EEPROM is

inhibited. When connected to V

DD

(and VCLK = V

DD

), the

EEPROM can be programmed. WP may not be left

open-circuit. WP input is a ‘don’t care’ in DDC1 mode.

6.8.5

T

EST

Pins 1 is a TEST pin for factory use only. It must be

connected to V

DD

in the application.

6.8.6

N

.

C

.

This pin has no connection and may be tied to V

SS

, V

DD

or

left open-circuit.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCB2421T | 1K dual mode serial EEPROM |

| PCD3344A | 8-BIT MICROCONTROLLER WITH DTMF GENERATOR |

| PCD3349AT | 8-BIT MICROCONTROLLER WITH DTMF GENERATOR |

| PCD3344AP | 8-BIT MICROCONTROLLER WITH DTMF GENERATOR |

| PCD3344AT | 8-BIT MICROCONTROLLER WITH DTMF GENERATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCB2421T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1K dual mode serial EEPROM |

| PCB2421TD-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

| PCB2510T1 | 制造商:BOBBIN 功能描述: |

| PCB258SX | 功能描述:線性和開(kāi)關(guān)式電源 230W Multiple Output RoHS:否 制造商:TDK-Lambda 產(chǎn)品:Switching Supplies 開(kāi)放式框架/封閉式:Enclosed 輸出功率額定值:800 W 輸入電壓:85 VAC to 265 VAC 輸出端數(shù)量:1 輸出電壓(通道 1):20 V 輸出電流(通道 1):40 A 商用/醫(yī)用: 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風(fēng)格:Rack 長(zhǎng)度: 寬度: 高度: |

| PCB266 | 制造商:Datak Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。