- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382378 > PCA9517DP (NXP SEMICONDUCTORS) Level translating I2C-bus repeater PDF資料下載

參數(shù)資料

| 型號(hào): | PCA9517DP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 其它接口 |

| 英文描述: | Level translating I2C-bus repeater |

| 中文描述: | SPECIALTY INTERFACE CIRCUIT, PDSO8 |

| 封裝: | 3 MM, PLASTIC, SOT-505-1, TSSOP-8 |

| 文件頁(yè)數(shù): | 4/13頁(yè) |

| 文件大?。?/td> | 107K |

| 代理商: | PCA9517DP |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

Philips Semiconductors

Product data sheet

PCA9517

Level translating I

2

C-bus repeater

2004 Oct 05

4

APPLICATION INFORMATION

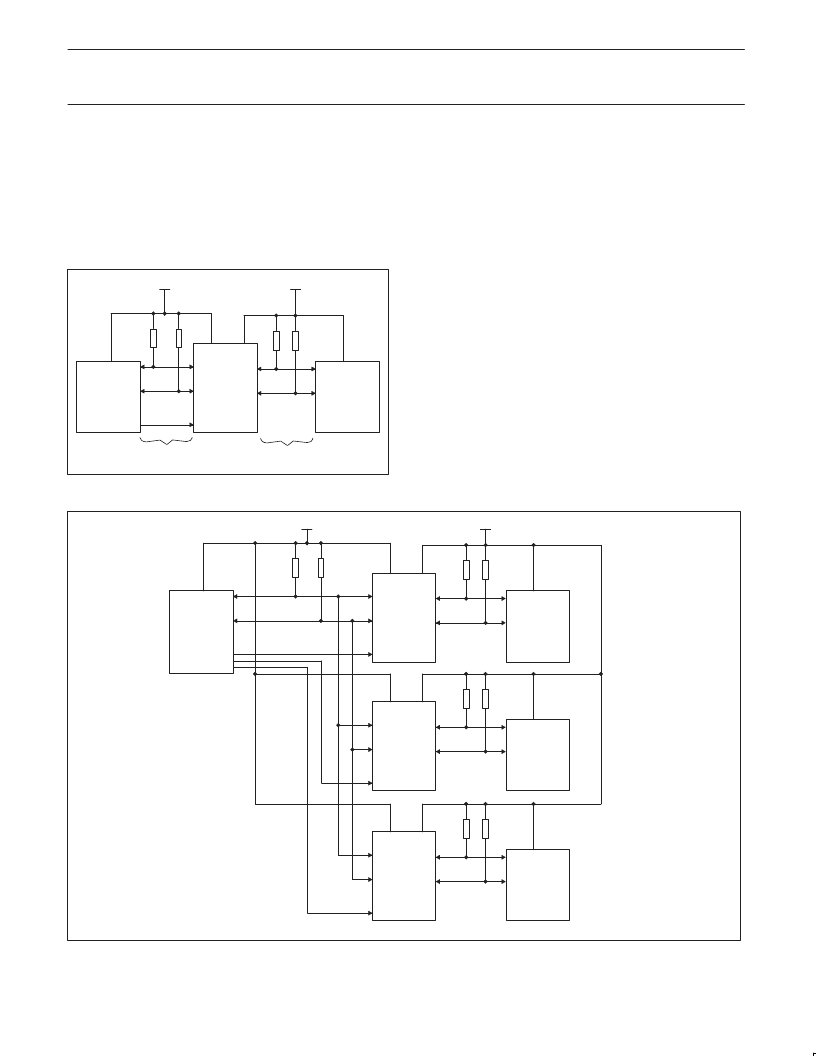

A typical application is shown in Figure 3. In this example, the

system master is running on a 3.3 V I

2

C-bus while the slave is

connected to a 1.2 V bus. Both buses run at 400 kHz. Master

devices can be placed on either bus.

The PCA9517 is 5 V tolerant so it does not require any additional

circuitry to translate between 0.9 V to 5.5 V bus voltages and

2.7 V to 5.5 V bus voltages.

SW02166

BUS B

BUS

MASTER

400 kHz

SLAVE

400 kHz

PCA9517

SDA

SDAB

SDA

SCL

SCLB

SCL

EN

BUS A

3.3 V

1.2 V

SDAA

SCLA

V

CCA

V

CCB

10 k

10 k

10 k

10 k

Figure 3. Typical application

When the A side of the PCA9517 is pulled LOW by a driver on the

I

2

C-bus, a comparator detects the falling edge when it goes below

0.3V

CCA

and causes the internal driver on the B side to turn on,

causing the B side to pull down to about 0.5 V. When the B side of

the PCA9517 falls, first a CMOS hysteresis type input detects the

falling edge and causes the internal driver on the A side to turn on

and pull the A side pin down to ground. In order to illustrate what

would be seen in a typical application, refer to Figures 6 and 7. If the

bus master in Figure 3 were to write to the slave through the

PCA9517, waveforms shown in Figure 6 would be observed on the

A bus. This looks like a normal I

2

C transmission except that the

HIGH level may be as low as 0.9 V, and the turn on and turn off of

the acknowledge signals are slightly delayed.

On the B bus side of the PCA9517, the clock and data lines would

have a positive offset from ground equal to the V

OL

of the PCA9517.

After the 8th clock pulse, the data line will be pulled to the V

OL

of the

slave device which is very close to ground in this example. At the

end of the acknowledge, the level rises only to the LOW level set by

the driver in the PCA9517 for a short delay while the A bus side

rises above 0.3V

CCA

then it continues HIGH. It is important to note

that any arbitration or clock stretching events require that the LOW

level on the B bus side at the input of the PCA9517 (V

IL

) be at or

below 0.4 V to be recognized by the PCA9517 and then transmitted

to the A bus side.

SW02347

BUS

MASTER

SLAVE

400 kHz

PCA9517

SDA

SDAA

SDA

SCL

SCLA

SCL

EN

V

CCA

V

CCB

SDAB

SCLB

10 k

10 k

10 k

10 k

SLAVE

400 kHz

PCA9517

SDAA

SDA

SCLA

SCL

EN

SDAB

SCLB

10 k

10 k

SLAVE

400 kHz

PCA9517

SDAA

SDA

SCLA

SCL

EN

SDAB

SCLB

10 k

10 k

Figure 4. Typical star application

Multiple PCA9517 A sides can be connected in a star configuration, allowing all nodes to communicate with each other.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCA9518 | Expandable 5-channel I2C hub |

| PCA9530 | 2-bit I2C LED dimmer |

| PCA9531 | 8-bit I2C LED dimmer |

| PCA9532 | 16-bit I2C LED dimmer |

| PCA9533 | 4-bit I2C LED dimmer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCA9517DP,118 | 功能描述:轉(zhuǎn)換 - 電壓電平 I2C BUS REPEATER RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時(shí)間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| PCA9517DP,118-CUT TAPE | 制造商:NXP 功能描述:PCA9517D Series 2.7 V to 5.5 V Level Translating I2C-Bus Repeater - TSSOP - 8 |

| PCA9517DP118 | 制造商:NXP Semiconductors 功能描述:IC I2C BUS REPEATER 5.5V 8TSSOP 制造商:NXP Semiconductors 功能描述:IC I2C BUS REPEATER 5.5V TSSOP-8 |

| PCA9517DP118 | 制造商:NXP Semiconductors 功能描述:IC I2C BUS REPEATER 5.5V TSSOP-8 |

| PCA9517DR | 功能描述:轉(zhuǎn)換 - 電壓電平 Lev-Translating I2C Bus Repeater RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時(shí)間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。