- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382377 > PCA8514 (NXP Semiconductors N.V.) Stand-alone OSD PDF資料下載

參數(shù)資料

| 型號(hào): | PCA8514 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Stand-alone OSD |

| 中文描述: | 單機(jī)OSD |

| 文件頁(yè)數(shù): | 46/64頁(yè) |

| 文件大?。?/td> | 322K |

| 代理商: | PCA8514 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

1995 Nov 27

46

Philips Semiconductors

Product specification

Stand-alone OSD

PCA8514

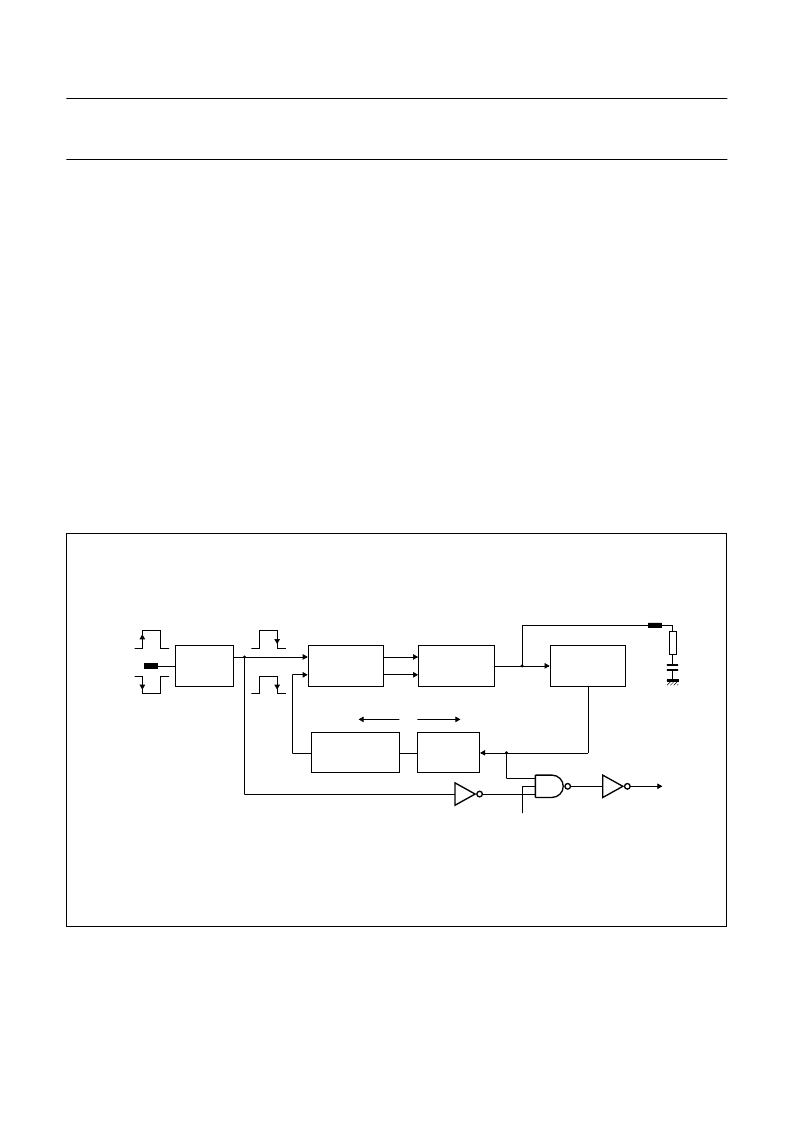

11 OSD CLOCK

The on-chip clock generator comprises Phase-Locked

Loop circuitry and is shown in Fig.39. The frequency of the

OSD clock is programmable and is determined by the

contents of the 6-bit counter, which is loaded using

Command 6. The OSD clock frequency is calculated as

shown below; frequencies within the range 4 to 14 MHz

can be selected.

Where: 16 < (PLLCN) < 40; (PLLCN) is the decimal value

held in the 6-bit counter.

The Voltage Controlled Oscillator (VCO) is synchronized

to the HIGH-to-LOW edge of f

1

(see Fig.39) which is

always on the trailing edge of f

HSYNC

. The programmable

active level detector will pass the HSYNC signal if it is

programmed as active HIGH or invert the HSYNC signal if

it is programmed as active LOW. The 4-bit prescaler

increments or decrements the output of the VCO in steps

of (16

×

f

HSYNC

).

f

OSD

f

HSYNC

16

PLLCN

(

)

×

×

=

The OSD clock is enabled/disabled using Command 7;

see Section 9.8. When the OSD clock is disabled, the

oscillator remains active, therefore the transient time from

the OSD clock start-up to locking into the external H

SYNC

signal is reduced. As the on-chip oscillator is always active

after power-on, when the OSD clock is enabled no large

currents flow (as for RC or LC oscillators); therefore

radiated noise is dramatically reduced.

Character width is a function of the OSD clock frequency;

decreasing f

OSD

increases the width of the characters.

Therefore, for optimum character display quality the

choice of the OSD clock frequency is important; this is

explained in Chapter 12.

Fig.39 Block diagram of OSD oscillator.

handbook, full pagewidth

MLC349

VOLTAGE

CONTROLLED

OSCILLATOR

CHARGE PUMP

AND

LOOP FILTER

PHASE/

FREQUENCY

DETECTOR

ACTIVE

LEVEL

DETECTOR

PROGRAMMABLE

6-BIT COUNTER

fOSD

divided by N

4-BIT

PRESCALER

HSYNC

OSD disable

fPLL

f1

C

R1

C1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCA8514P | Stand-alone OSD |

| PCA8514T | Stand-alone OSD |

| PCA8515 | Stand-alone OSD |

| PCA8515P | Stand-alone OSD |

| PCA8515T | Stand-alone OSD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCA8514P | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Stand-alone OSD |

| PCA8514T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Stand-alone OSD |

| PCA8515 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Stand-alone OSD |

| PCA8515P | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Stand-alone OSD |

| PCA8515T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Stand-alone OSD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。