- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367723 > P83CE560 (NXP Semiconductors N.V.) 8-BIT SINGLE CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | P83CE560 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-BIT SINGLE CHIP MICROCONTROLLERS |

| 中文描述: | 8位單晶片微控制器 |

| 文件頁數(shù): | 23/84頁 |

| 文件大小: | 441K |

| 代理商: | P83CE560 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

1997 Aug 01

23

Philips Semiconductors

Product specification

8-bit microcontroller

P8xCE560

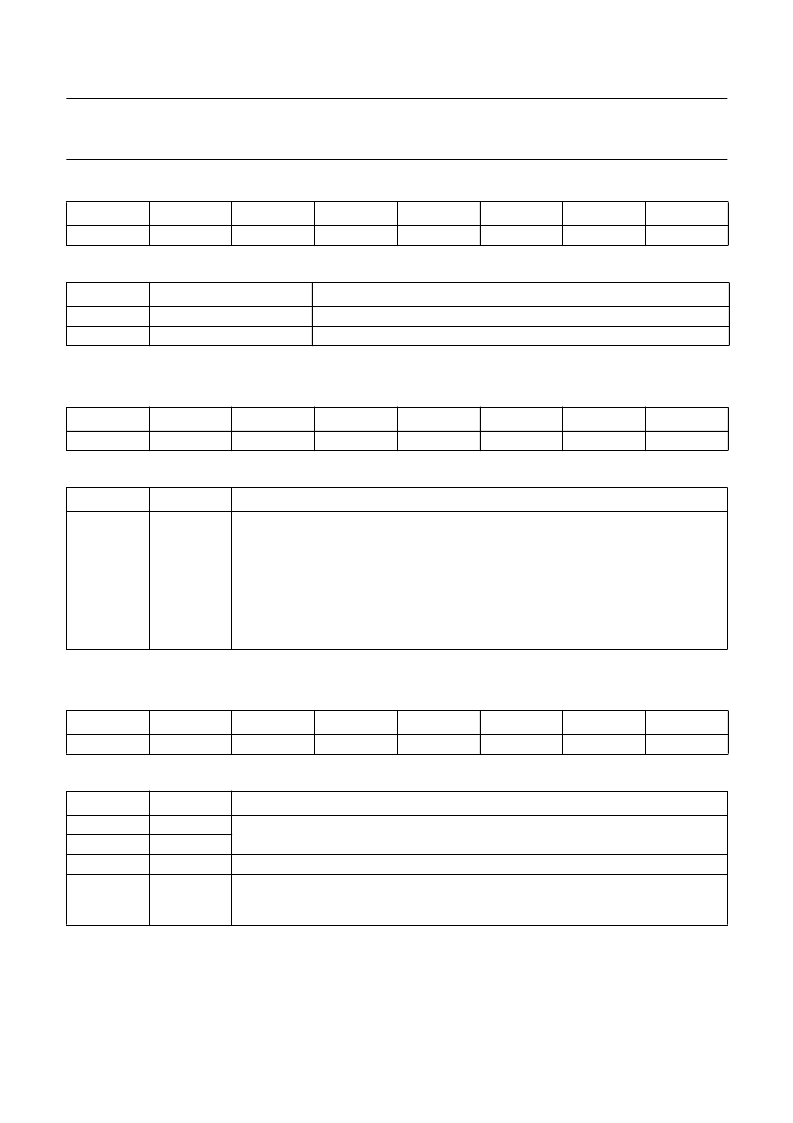

Table 17

ADC Result Register High Bits; ADRSH (address F7H)

Table 18

Description of ADRSH bits

11.8.2

ADC I

NPUT

P

ORT

S

CAN

-S

ELECT

R

EGISTER

(ADPSS)

Table 19

ADC Input Port Scan-Select Register (address E7H)

Table 20

Description of ADPSS bits

11.8.3

ADC C

ONTROL

R

EGISTER

(ADCON)

Table 21

ADC Control Register (address D7H)

Table 22

Description of ADCON bits

7

6

5

4

3

2

1

0

0

0

0

0

0

0

ADRSn.9

ADRSn.8

BIT

SYMBOL

DESCRIPTION

7 to 2

1 to 0

The upper 6 bits ADRSH.2 to ADRSH.7 are always read as a logic 0.

ADC result upper 2 bits.

ADRSn.9 to ADRSn.8

7

6

5

4

3

2

1

0

ADPSS7

ADPSS6

ADPSS5

ADPSS4

ADPSS3

ADPSS2

ADPSS1

ADPSS0

BIT

SYMBOL

DESCRIPTION

7 to 0

ADPSS7

to

ADPSS0

Control bits to select the analog input channel(s) to be scanned for

analog-to-digital conversion. If all bits ADPSS0 to ADPSS7 = 0, then no conversion can

be started. If ADPSS is written while an analog-to-digital conversion is in progress

(ADSST = 1; ADCON.3) then the autoscan loop with the previous selected analog

inputs is completed first. The next autoscan loop is performed with the new selected

analog inputs. For each individual bit position ADPSSn (n = 0 to 7):

If ADPSSn = 0, then the corresponding analog input is skipped in the autoscan loop

If ADPSSn = 1, then the corresponding analog input is included in the autoscan loop.

7

6

5

4

3

2

1

0

ADPR1

ADPR0

ADPOS

ADINT

ADSST

ADCSA

ADSRE

ADSFE

BIT

SYMBOL

DESCRIPTION

7

6

5

4

ADPR1

ADPR0

ADPOS

ADINT

These two bits determine the value of the prescaler divisor (m); see Table 23.

ADPOS is reserved for future use. Must be a logic 0 if ADCON is written.

ADC interrupt.

This flag is set when all selected analog inputs are converted (both in

continuous scan and in one-time scan mode). An interrupt is invoked if this interrupt flag

is enabled. ADINT must be cleared by software. It cannot be set by software.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P87CE560 | 8-BIT SINGLE CHIP MICROCONTROLLERS |

| P80CE560EFB | 8-BIT MICROCONTROLLER |

| P83CE560EFB | NPN Silicon Power Transistor, TO-220F-3SL |

| P80CE598FHB | 8-bit microcontroller with CAN controller(帶CAN控制器的8位微控制器) |

| P83CE598FFB | 8-bit microcontroller with CAN controller(帶CAN控制器的8位微控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83CE560EFB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller |

| P83CE560EFB/081,55 | 制造商:NXP Semiconductors 功能描述:- Tape and Reel |

| P83CE560EFB/NNN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P83CE598 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with on-chip CAN |

| P83CE598FFB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with on-chip CAN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。