P10C68/P11C68

6

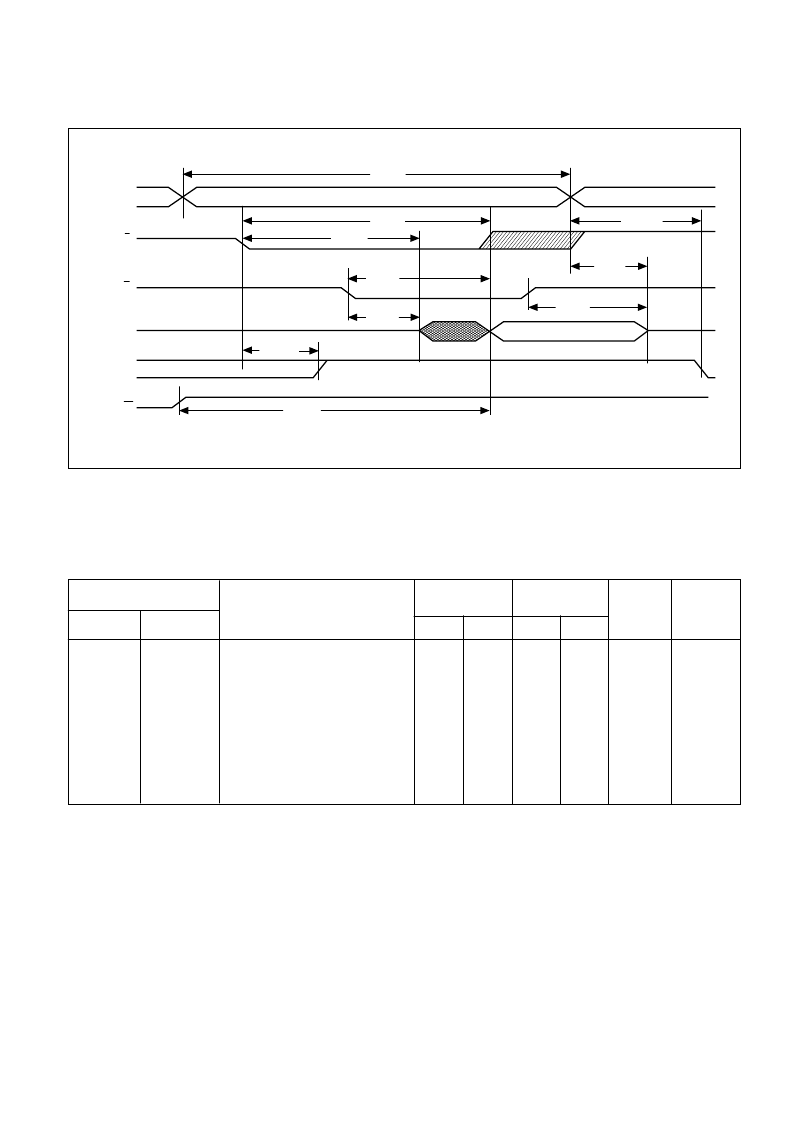

WRITE CYCLE 1 : W (BAR) CONTROLLED

(See notes 8 and 13)

Commercial and Industrial Temperature Range

t

WHQV

W

t

AVAV

t

ELQV

t

ELQX

t

EHICCL

t

EHQZ

t

GHQZ

t

GLQX

t

ELICCH

DATA VALID

STANDBY

ACTIVE

DQ (DATA OUT)

ADDRESS

E

G

I

CC

t

GLQV

F

igure 5. READ CYCLE 2 timing diagram (see note 9).

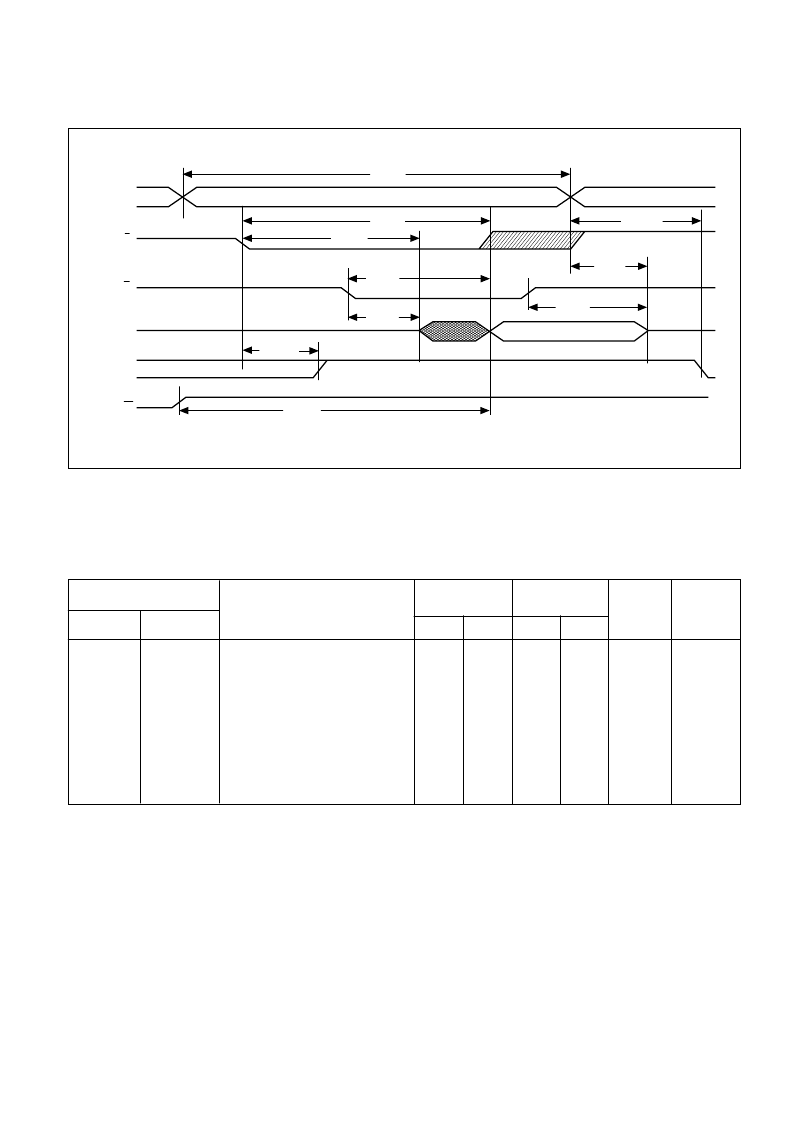

Standard

t

AVAV

t

WLWH

t

ELWH

t

DVWH

t

WHDX

t

AVWH

t

AVWL

t

WHAX

t

WLQZ

t

WHQZ

Alternative

t

WC

t

WP

t

CW

t

DW

t

DH

t

AW

t

AS

t

WR

t

WZ

t

OW

Parameter

Write cycle time

Write pulse width

Chip enable to end of write

Data set-up to end of write

Data hold after end of write

Address set-up to end of write

Address set-up to start of write

Address hold after end of write

Write enable to output disable

Output active after end of write

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes

11, 14

P10C68-45

P11C68-45

Min.

P10C68-35

P11C68-35

Min.

Symbol

45

35

35

30

0

35

0

0

5

Max.

35

45

35

35

30

0

35

0

0

5

Max.

35

NOTES

13.

14.

E (bar) or W (bar) must be

≥

VIH during address transitions.

If W (bar) is low when E (bar) goes low, the outputs remain in the high impedance state.