- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄359235 > MT9300B (Zarlink Semiconductor Inc.) Multi-Channel Voice Echo Canceller PDF資料下載

參數(shù)資料

| 型號(hào): | MT9300B |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Multi-Channel Voice Echo Canceller |

| 中文描述: | 多通道語(yǔ)音回聲消除器 |

| 文件頁(yè)數(shù): | 13/39頁(yè) |

| 文件大小: | 629K |

| 代理商: | MT9300B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

MT9300B

Data Sheet

13

Zarlink Semiconductor Inc.

Device Configuration

The MT9300B architecture contains 32 echo cancellers divided into 16 groups. Each group has two echo

cancellers which can be individually controlled (Echo Canceller A and B). They can be set in three distinct

configurations:

Normal, Back-to-Back,

and

Extended Delay

. See Figure 6.

Normal Configuration

In Normal configuration, the two echo cancellers (Echo Canceller A and B) are positioned in parallel, as shown in

Figure 6a, providing 64 milliseconds of echo cancellation in two channels simultaneously.

Back-to-Back Configuration

In Back-to-Back configuration, the two echo cancellers from the same group are positioned to cancel echo coming

from both directions in a single channel providing full-duplex 64 ms echo cancellation. See Figure 6c. This

configuration uses only one timeslot on PORT1 and PORT2 and the second timeslot normally associated with ECB

contains undefined data. Back-to-Back configuration allows a no-glue interface for applications where bidirectional

echo cancellation is required.

Back-to-Back configuration is selected by writing “1” into the BBM bit of

both

Control Register A1 and Control

Register B1 of a given group of echo cancellers. Table 2 shows the 16 groups of 2 cancellers that can be configured

into Back-to-Back.

Examples of Back-to-Back configuration include positioning one group of echo cancellers between a CODEC and a

transmission device or between two codecs for echo control on analog trunks.

Extended Delay Configuration

In this configuration, the two echo cancellers from the same group are internally cascaded into one 128

milliseconds echo canceller. See Figure 6b. This configuration uses only one timeslot on PORT1 and PORT2 and

the second timeslot normally associated with ECB contains undefined data.

Extended Delay configuration is selected by writing “1” into the ExtDl bit in Echo Canceller A, Control Register A1.

For a given group, only Echo Canceller A, Control Register A1, has the ExtDl bit. Control Register B1, bit-0 must

always be set to zero.

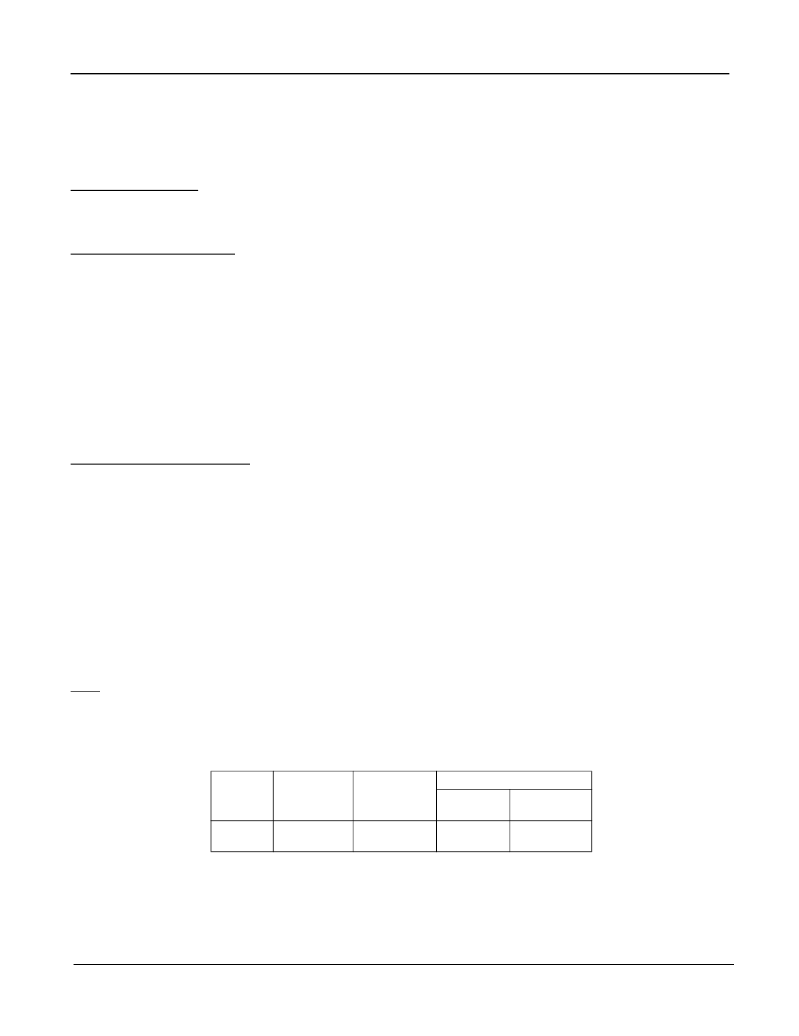

Table 2 shows the 16 groups of 2 cancellers that can each be configured into 64 ms or 128 ms echo tail capacity.

Echo Canceller Functional States

Each echo canceller has four functional states:

Mute, Bypass, Disable Adaptation

and

Enable Adaptation

.

Mute

In Normal and in Extended Delay configurations, writing a “1” into the MuteR bit replaces Rin with quiet code which

is applied to both the Adaptive Filter and Rout. Writing a “1” into the MuteS bit replaces the Sout PCM data with

quiet code.

LINEAR

16 bits

2’s

complement

SIGN/

-

Law

A-Law

MAGNITUDE

CCITT (G.711)

μ

-

Law

A-Law

+Zero

(quiet code)

0000h

80h

FFh

D5h

Table 1 - Quiet PCM Code Assignment

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9300BL | Multi-Channel Voice Echo Canceller |

| MT9300BV | Multi-Channel Voice Echo Canceller |

| MT9315 | CMOS Acoustic Echo Canceller |

| MT933 | 3.3V 10/100 Fast Ethernet Transceiver to MII |

| MT933CG | 3.3V 10/100 Fast Ethernet Transceiver to MII |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9300BL | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel Voice Echo Canceller |

| MT9300BV | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel Voice Echo Canceller |

| MT9315 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:CMOS Acoustic Echo Canceller |

| MT9315AE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:CMOS Acoustic Echo Canceller |

| MT9315AP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:CMOS Acoustic Echo Canceller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。