- 您現(xiàn)在的位置:買賣IC網 > PDF目錄383643 > MT8977 (Mitel Networks Corporation) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數資料

| 型號: | MT8977 |

| 廠商: | Mitel Networks Corporation |

| 元件分類: | 通信及網絡 |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數: | 16/26頁 |

| 文件大小: | 344K |

| 代理商: | MT8977 |

MT8977

ISO-CMOS

Preliminary Information

4-114

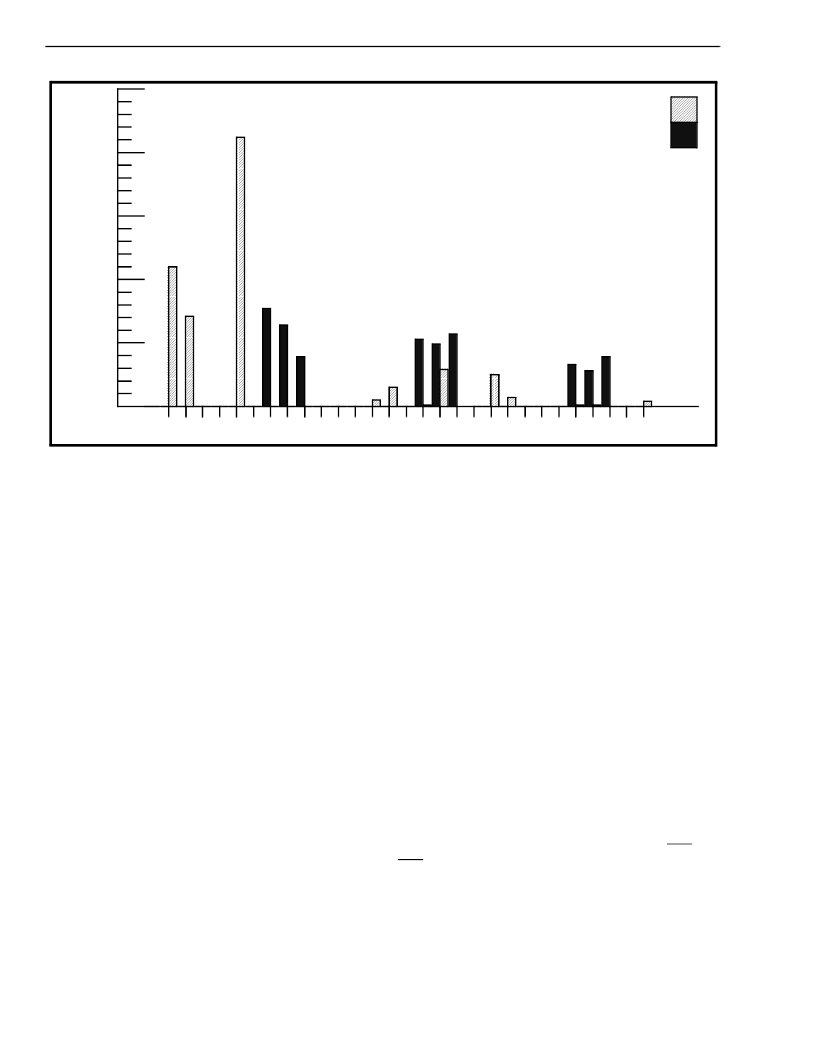

Figure 10 - Reframe Time

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AA

AA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AA

AA

AA

AA

AA

AA

AA

AAA

AAA

AAA

AA

AA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AA

AA

AA

AA

AA

AA

D4

ESF

Percentage Reframe Time Probability Versus Reframe Time

With Pseudo Random Data

50

40

30

20

10

0

%

0

7

8

10

12

14

16

Reframe Time (msec)

18

20

22

24

26

28

30

32

34

The out of sync threshhold can be changed from 2

out of 4 errors in F

T

(or FPS) to 4 out of 12 errors in

F

T

(or FPS). The average reframe time is 24 ms for

ESF mode, and 12ms for D3/D4 modes.

Figure 10 is a bar graph which shows the probability

of achieving frame synchronization at a specific time.

The chart shows the results for ESF mode with CRC

check, and D3/D4 modes of operation. The average

reframe time with random data is 24 ms for ESF, and

13 msec. D3/D4 modes. The probability of a reframe

time of 35 ms or less is 88% for ESF mode, and

97% for D3/D4 modes. In ESF mode it is

recommended that the CRC check be enabled

unless the line has a high error rate. With the CRC

check disabled the average reframe time is greater

because the framer must also check for mimics.

Applications

Figure 11 shows the external components that are

required in a typical ESF application. The MT8980 is

used to control and monitor the device as well as

switch data to DSTi and DSTo. The MT8952, the

HDLC protocol controller, is shown in this application

to illustrate how the data on the FDL could be used.

The digital phase-locked loop, the MT8940/41,

provides all the clocks necessary to make a

functional interface. The clock input to the MT8977

at E1.5i is extracted from the received data signal

with an external circuit. The E1.5i clock is internally

divided by 193 to obtain an 8 kHz clock which is

output at E8Ko. The MT8940 uses this 8 kHz signal

to provide a phase locked 2.048 MHz clock for the

ST-BUS interface and a 1.544 MHz clock for the DS1

transmit side. Using the 8 kHz signal as a reference

for the MT8940/41 DPLL effectively filters out the

high frequency jitter in the extracted clock. Thus, the

C2 and C1.5 clocks generated by the MT8940/41 will

have significantly lower jitter than would be the case

if the extracted 1.5 MHz clock was used as a

reference directly.

An external line driver circuit is required in order to

interface the device to twisted pair cabling. The split

phase unipolar signals output by the MT8977 at TxA

and TxB are used by the line driver circuit to

generate a bipolar AMI signal. The line driver is

transformer coupled to an equalization circuit and

the DS1 line. Equalization of the transmitted signal

is

required

to

meet

crossconnect compatible equipment (see ANSI

T1.102 and AT & T Technical Advisory #34). On the

receive side the bipolar line signal is converted into

a unipolar format by the line receiver circuit. The

resulting split phase signals are input at the RxA and

RxB pins on the MT8977. The signals are combined

together to produce a composite return to zero signal

which is clocked into the device at RxD. An

uncommitted nand gate in the MT8940/41 can be

used for this purpose.

the

specifications

for

The MT8977 can be interfaced to a high speed

parallel bus or to a microprocessor using the

MT8920B Parallel Access Circuit (STPA). Figure 11

相關PDF資料 |

PDF描述 |

|---|---|

| MT8977AC | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT8977AE | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT8977AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT8979 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT8979 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MT8977AC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/ESF Framer Circuit |

| MT8977AE | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/ESF Framer Circuit |

| MT8977AP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Mitel Networks Corporation 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: 制造商:ZARLINK 功能描述: |

| MT8977APR | 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: 制造商:ZARLINK 功能描述: |

| MT8979 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY CEPT PCM 30/CRC-4 Framer & Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復。