- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383642 > MT8930C (Mitel Networks Corporation) CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information PDF資料下載

參數(shù)資料

| 型號(hào): | MT8930C |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| 中文描述: | 意法半導(dǎo)體的CMOS總線⑩家庭用戶網(wǎng)絡(luò)接口電路的初步信息 |

| 文件頁數(shù): | 8/42頁 |

| 文件大小: | 323K |

| 代理商: | MT8930C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

MT8930C

9-40

Line Code

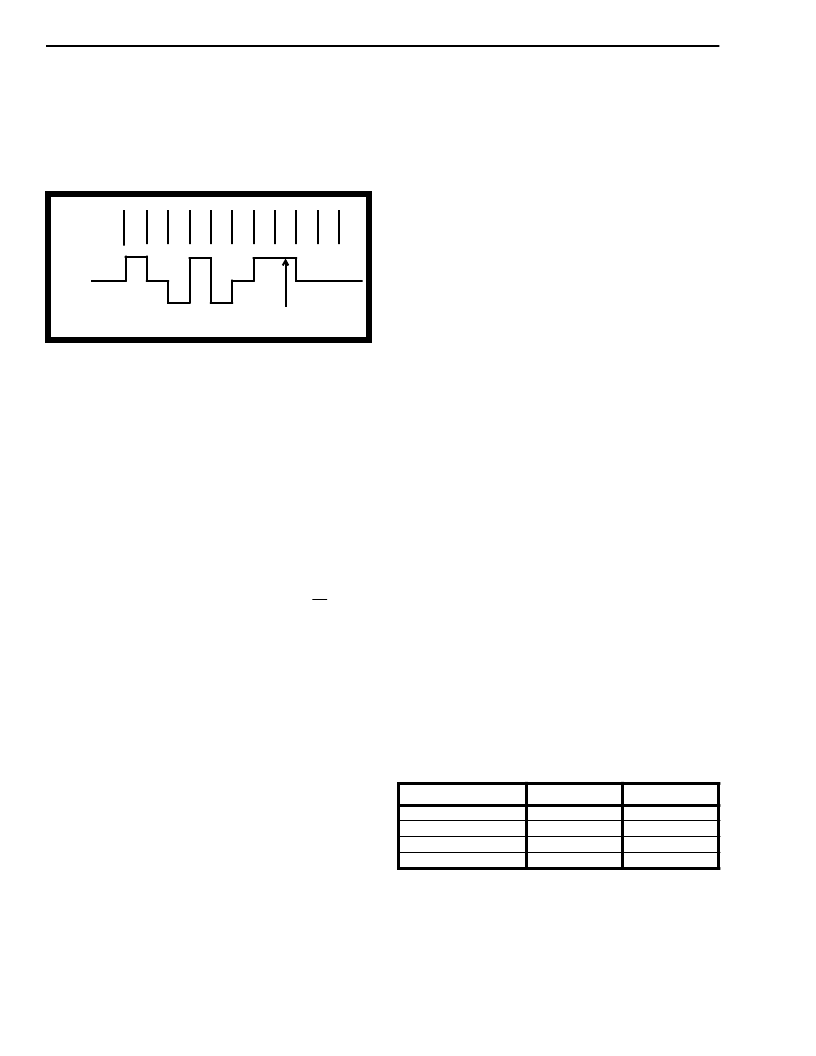

The line code used on the S-interface is a Pseudo

ternary code with 100% pulse width as seen in

Figure 6 below. Binary zeros are represented as

marks on the line and successive marks will

alternate in polarity.

Figure 6 - Alternate Zero Inversion Line Code

A mark which does not adhere to the alternating

polarity is known as a bipolar violation.

Framing

The valid frame structure transmitted by the NT and

TE contains the following (refer Fig. 5):

NT to TE:

- Framing bit (F)

- B1 and B2 channels (B1,B2)

- DC balancing bits (L)

- D-channel bits (D0, D1)

- Auxiliary framing and N bit (Fa, N), N=Fa

- Activation bit (A)

- D-echo channel bits (E)

- Multiframing bit (M)

- S-channel bit

TE to NT:

- Framing bit (F)

- B1 and B2 channels (B1, B2)

- DC balancing bits (L)

- D-channel bits (D0, D1)

- Auxiliary framing bit (Fa) or Q-channel bit

The framing mechanism on the S-interface makes

use of line code violations to identify frame

boundaries. The F-bit violates the alternating

line code sequence to allow for quick identification of

the frame boundaries. To secure the frame

alignment, the next mark following the frame

balancing bit (L) will also produce a line code

violation. If the data following the balancing bit is all

binary ones, the zero in the auxiliary framing bit (Fa)

or N-bit (for the direction NT to TE) will provide

successive violations to ensure that the 14 bit

criterion (13 bit criterion in the direction TE to NT)

specified in Recommendations I.430 and T1.605 is

satisfied. If the B1-channel is not all binary ones, the

first zero following the L-bit will violate the line code

sequence, thus allowing subsequent marks to

alternate without bipolar violations.

The Fa and N bits can also be used to identify a

multiframe structure (when this is done, the 14 bit

criterion may not be met). This multiframe structure

will make provisions for a low speed signalling

channel to be used in the TE to NT direction

(Q-channel). It will consist of a five frame multiframe

which can be identified by the binary inversion of the

Fa and N-bit on the first frame and consequently on

every fifth frame of the multiframe. Upon detection of

the multiframe signal, the TE will replace the next Fa-

bit to be transmitted with the Q-bit.

The DC balancing bits (L) are used to remove any

DC content from the line. The balancing bit will be a

mark if the number of preceding marks up to the

previous balancing bit is odd. If the number of

marks is even, the L-bit will be a space.

The A-bit is used by the NT during line activation

procedures (refer to state activation diagrams). The

state of the A-bit will advise the TE if the NT has

achieved synchronization.

The E-bit is the D-echo channel. The NT will reflect

the binary value of the received D-channel into the

E-bits. This is used to establish the access

contention

resolution

in

configuration. This is described in more detail in the

section of the D-channel priority mechanism.

a

point-to-multipoint

The M-bit is a second level of multiframing which is

used for structuring the Q-bits. The frame with M-

bit=1 identifies frame #1 in the twenty frame

multiframe. The Q-channel is then received as

shown in Table 1. All synchronization with the

multiframes must be performed externally.

Table 1. Q-channel Allocation

Bit Order

When using the B-channels for PCM voice, the first

bit to be transmitted on the S-Bus should be the sign

bit. This complies with the existing telecom

standards which transmit PCM voice as most

significant bit first. However, if the B-channels are to

BINARY

VALUE

LINE

SIGNAL

Violation

0

1

0

0

0

1

0

0

1

1

FRAME #

1

6

11

16

Q-Bit

Q1

Q2

Q3

Q4

M-Bit

1

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8930CC | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8930CE | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8930CP | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8931C | Subscriber Network Interface Circuit(用戶網(wǎng)絡(luò)接口電路(提供點(diǎn)到點(diǎn)或點(diǎn)到多點(diǎn)數(shù)字傳送)) |

| MT8940 | T1/CEPT Digital Trunk PLL(T1/CEPT數(shù)字中繼鎖相環(huán)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8930C-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8930CC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8930CE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CPR | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。