- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45372 > MPC8569EVTANKGB (FREESCALE SEMICONDUCTOR INC) RISC PROCESSOR, PBGA783 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC8569EVTANKGB |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISC PROCESSOR, PBGA783 |

| 封裝: | 29 X 29 MM, 1 MM PITCH, PLASTIC, BGA-783 |

| 文件頁數(shù): | 100/126頁 |

| 文件大小: | 2847K |

| 代理商: | MPC8569EVTANKGB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁當(dāng)前第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

HDLC, BISYNC, Transparent, and Synchronous UART Interfaces

MPC8569E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 0

Freescale Semiconductor

75

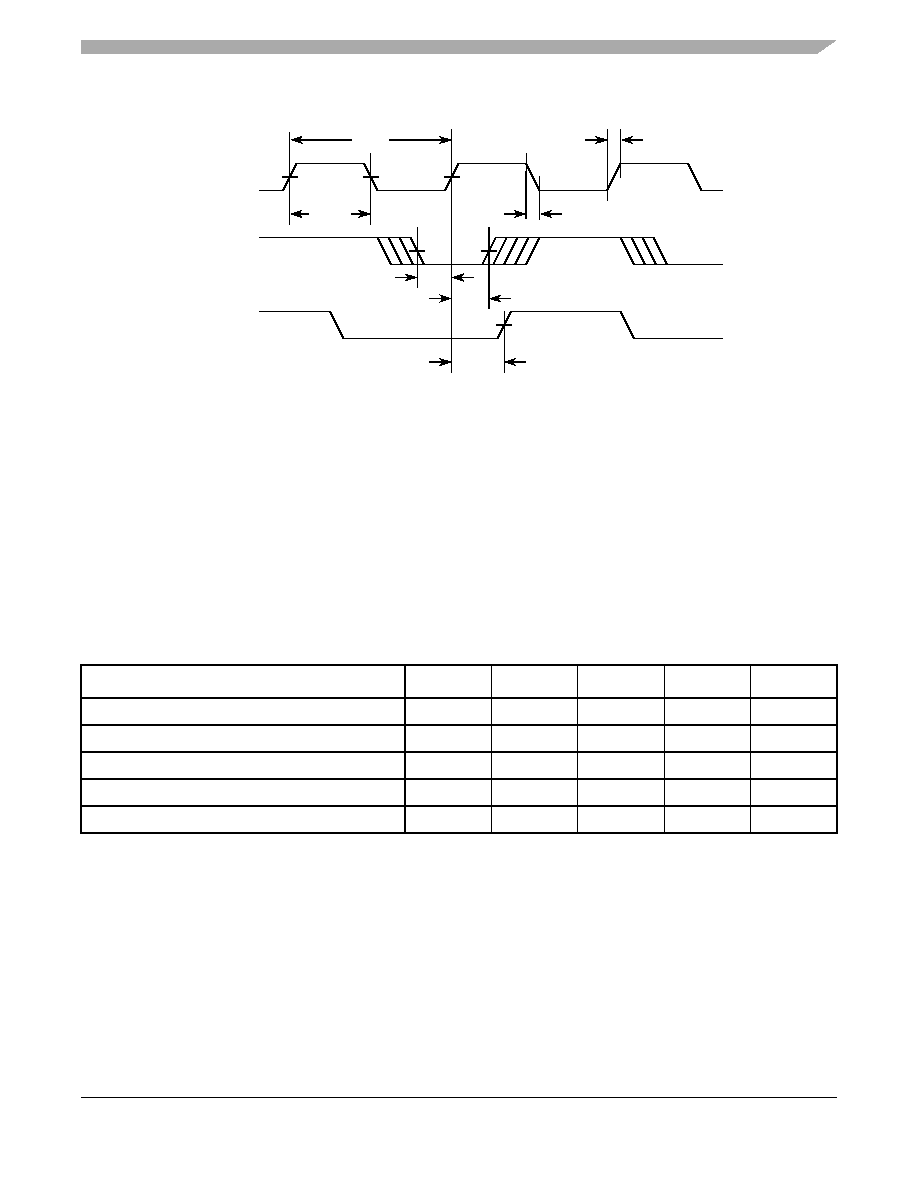

The following figure shows the MII management AC timing diagram.

Figure 34. MII Management Interface Timing Diagram

2.8

HDLC, BISYNC, Transparent, and Synchronous UART Interfaces

This section describes the DC and AC electrical specifications for the high level data link control (HDLC), BISYNC,

transparent, and synchronous UART interfaces of the MPC8569E.

2.8.1

HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical

Characteristics

The following table provides the DC electrical characteristics for the HDLC, BISYNC, Transparent, and synchronous UART

interfaces.

Table 43. HDLC, BISYNC, and Transparent DC Electrical Characteristics

For recommended operating conditions, see Table 3

Parameter

Symbol

Min

Max

Unit

Notes

Input high voltage

VIH

2—

V

1

Input low voltage

VIL

—0.8

V

1

Input current (OVIN = 0 V or OVIN = OVDD)IIN

—±40

μA2

Output high voltage (OVDD = min, IOH = –2 mA)

VOH

2.4

—

V

—

Output low voltage (OVDD = min, IOL = 2 mA)

VOL

—0.4

V

—

Note:

1. The min VILand max VIH values are based on the respective min and max OVIN values found in Table 3.

MDC

tMDDXKH

tMDC

tMDCH

tMDCR

tMDCF

tMDKHDX

MDIO

(Input)

(Output)

tMDDVKH

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。