- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369927 > MPC8272 (Motorola, Inc.) MPC8272 PowerQUICC II Family Hardware Specifications PDF資料下載

參數(shù)資料

| 型號: | MPC8272 |

| 廠商: | Motorola, Inc. |

| 英文描述: | MPC8272 PowerQUICC II Family Hardware Specifications |

| 中文描述: | MPC8272的PowerQUICC II系列硬件規(guī)格 |

| 文件頁數(shù): | 3/56頁 |

| 文件大小: | 1090K |

| 代理商: | MPC8272 |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

MOTOROLA

MPC8272 PowerQUICC II Family Hardware Specifications

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

3

Overview

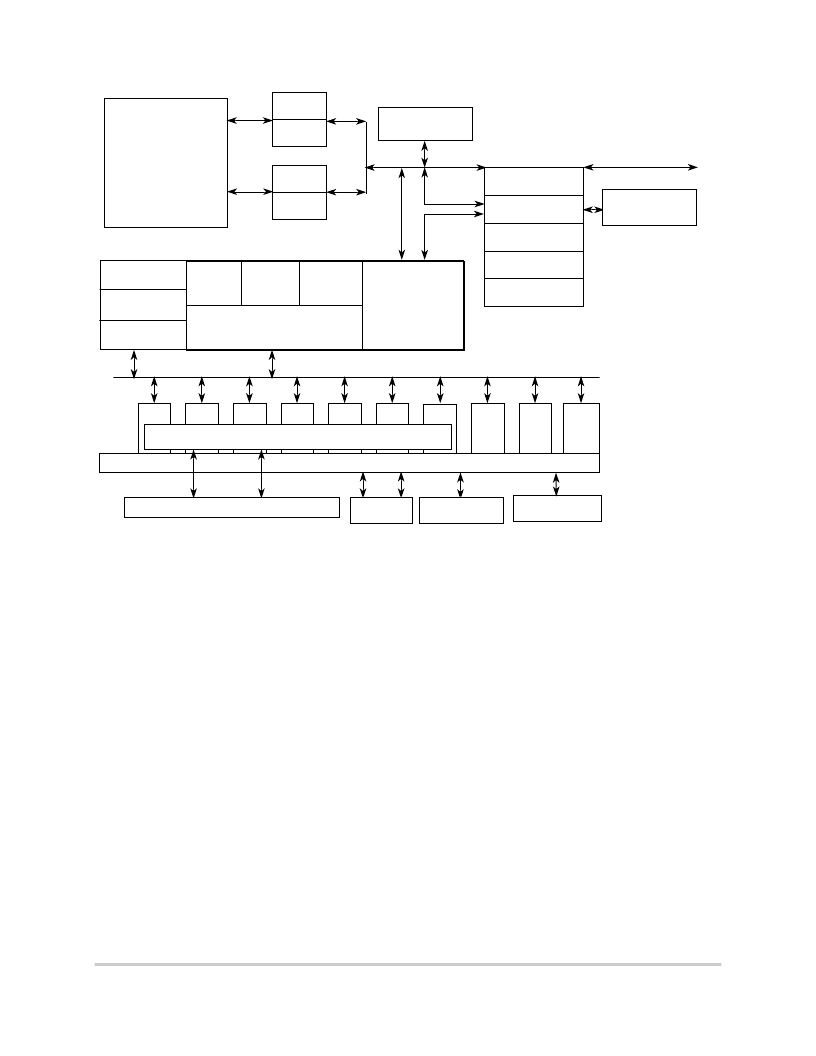

Figure 1. Block Diagram

1.1

Features

The major features of the MPC8272 are as follows:

Dual-issue integer (G2_LE) core

— A core version of the MPC603e microprocessor

— System core microprocessor supporting frequencies of 266-400 MHz

— Separate 16-Kbyte data and instruction caches:

– Four-way set associative

– Physically addressed

– LRU replacement algorithm

— PowerPC architecture-compliant memory management unit (MMU)

— Common on-chip processor (COP) test interface

— Supports bus snooping for cache coherency

— Floating-point unit (FPU) supports floating-point arithmetic

— Support for cache locking

Low-power consumption

Separate power supply for internal logic (1.5 V) and for I/O (3.3 V)

16 Kbytes

I-Cache

G2_LE Core

I-MMU

16 Kbytes

D-Cache

D-MMU

Communication Processor Module (CPM)

Timers

Parallel I/O

Baud Rate

Generators

32-bit RISC Microcontroller

and Program ROM

Serial

DMA

60x-to-PCI

Bridge

Memory Controller

Clock Counter

System Functions

System Interface Unit

(SIU)

PCI Bus

32 bits, up to 66 MHz

FCC1

FCC2

SCC1

SCC3

SCC4

SMC1

SMC2

SPI

I

2

C

2 MII/RMII

Ports

Port

60x Bus

Interrupt

Controller

Time Slot Assigner

2 TDM Ports

Non-Multiplexed

I/O

Bus Interface Unit

Virtual

IDMAs

16 KB

Data

RAM

Security (SEC)

1

2

1 8-bit Utopia

Serial interfSerial Interface

4 KB

Instruction

RAM

Note

1

MPC8272/8248 only

2

MPC8272/8271 only

USB 2.0

F

Freescale Semiconductor, Inc.

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8272VR | MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8260AEC | MPC826xA (HiP4) Family Hardware Specifications |

| MPC826XACZUBUS | MPC826xA (HiP4) Family Hardware Specifications |

| MPC826XACZUBUSX | MPC826xA (HiP4) Family Hardware Specifications |

| MPC826XACZUSPM | MPC826xA (HiP4) Family Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8272_06 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

| MPC8272ADS | 功能描述:開發(fā)板和工具包 - 其他處理器 DEVELOPMENT SYSTEM FOR A RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| MPC8272CVR | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8272CVRB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

| MPC8272CVRE | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。