- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369925 > MPC8248ZQI (Motorola, Inc.) MPC8272 PowerQUICC II Family Hardware Specifications PDF資料下載

參數(shù)資料

| 型號: | MPC8248ZQI |

| 廠商: | Motorola, Inc. |

| 英文描述: | MPC8272 PowerQUICC II Family Hardware Specifications |

| 中文描述: | MPC8272的PowerQUICC II系列硬件規(guī)格 |

| 文件頁數(shù): | 19/56頁 |

| 文件大小: | 539K |

| 代理商: | MPC8248ZQI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

19

MPC8272 PowerQUICC II Family Hardware Specifications

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

AC Electrical Characteristics

6.2

SIU AC Characteristics

Table 11 lists SIU input characteristics.

NOTE: PCI AC Timing

The MPC8272 meets the timing requirements of

PCI Specification

Revision 2.2

. Refer to Section 7, “Clock Configuration Modes” and “Note:

Tval (Output Hold)” to determine if a specific clock configuration is

compliant.

Table 12 lists SIU output characteristics.

NOTE

Activating data pipelining (setting BR

x

[DR] in the memory controller)

improves the AC timing.

Figure 9 shows the interaction of several bus signals.

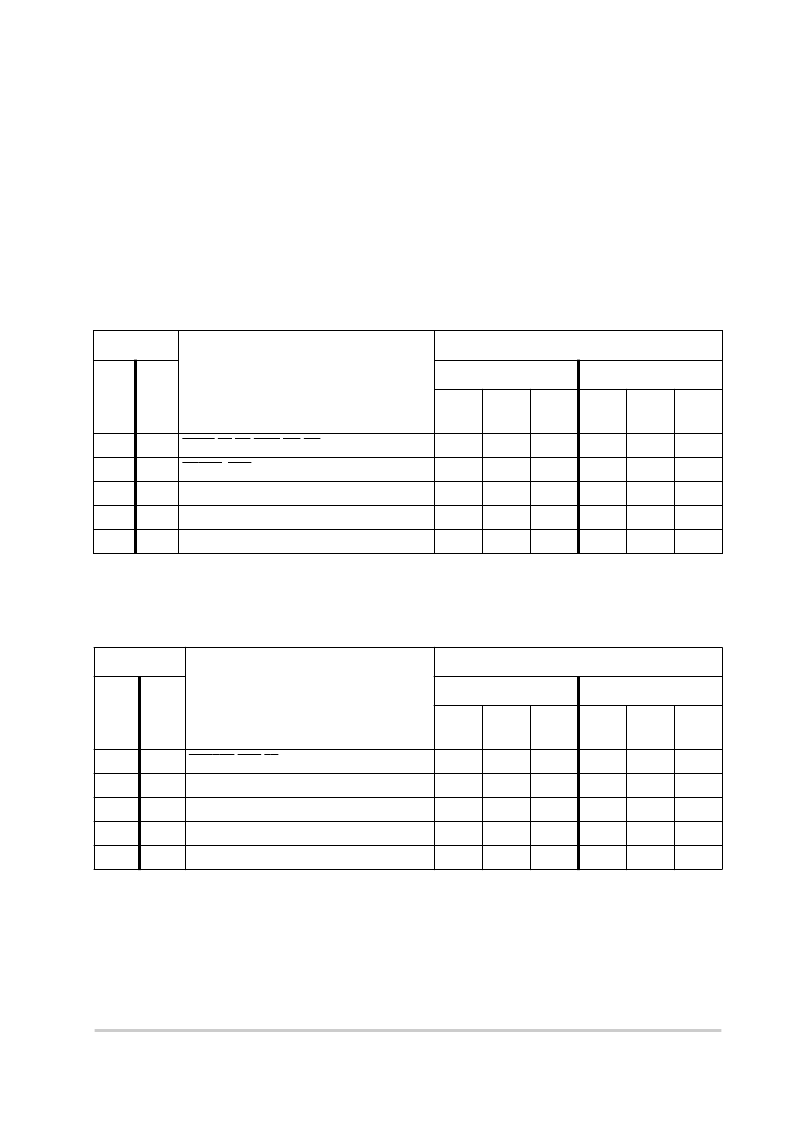

Table 11. AC Characteristics for SIU Inputs

1

1

Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings

are measured at the pin.

Spec Number

Characteristic

Value (ns)

Setup

Hold

Setup

Hold

66

MHz

83

MHz

100

MHz

66

MHz

83

MHz

100

MHz

sp11

sp10

AACK/TA/TS/DBG/BG/BR

6

5

3.5

0.5

0.5

0.5

sp11a

sp10

ARTRY/ TEA

6

5

4

0.5

0.5

0.5

sp12

sp10

Data bus in normal mode

5

4

3.5

0.5

0.5

0.5

sp13

sp10

Data bus in pipeline mode

5

4

2.5

0.5

0.5

0.5

sp15

sp10

All other pins

5

4

3.5

0.5

0.5

0.5

Table 12. AC Characteristics for SIU Outputs

1

1

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal.

Timings are measured at the pin.

2

To achieve 1 ns of hold time at 66.67/83.33/100 MHZ, a minimum loading of 20 pF is required.

Spec Number

Characteristic

Value (ns)

Max

Min

Maximum Delay

Minimum Delay

66

MHz

83

MHz

100

MHz

66

MHz

83

MHz

100

MHz

sp31

sp30 PSDVAL/TEA/TA

7

6

5.5

1

1

1

sp32

sp30

ADD/ADD_atr./BADDR/CI/GBL/WT

8

6.5

5.5

1

1

1

sp33

sp30 Data bus

2

6.5

6.5

5.5

0.5

0.5

0.5

sp34

sp30

Memory controller signals/ALE

6

5.5

5.5

1

1

1

sp35

sp30

All other signals

6

5.5

5.5

1

1

1

F

Freescale Semiconductor, Inc.

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8248ZQM | MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8248ZQP | MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8248ZQT | MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8271CVR | MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8271CVRB | MPC8272 PowerQUICC II Family Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8248ZQM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

| MPC8248ZQMIBA | 功能描述:微處理器 - MPU PQ27E A W/ TALITOS RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8248ZQP | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8248ZQPIEA | 功能描述:微處理器 - MPU PQ27E A W/ TALITOS RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8248ZQT | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。