- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369919 > MMC2075 (Motorola, Inc.) Integrated Processor with Roaming FLEX Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | MMC2075 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Integrated Processor with Roaming FLEX Decoder |

| 中文描述: | 綜合處理器漫游FLEX解碼器 |

| 文件頁數(shù): | 23/34頁 |

| 文件大小: | 768K |

| 代理商: | MMC2075 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

Tables of Signals

Signal and Connection Descriptions

Preliminary

23

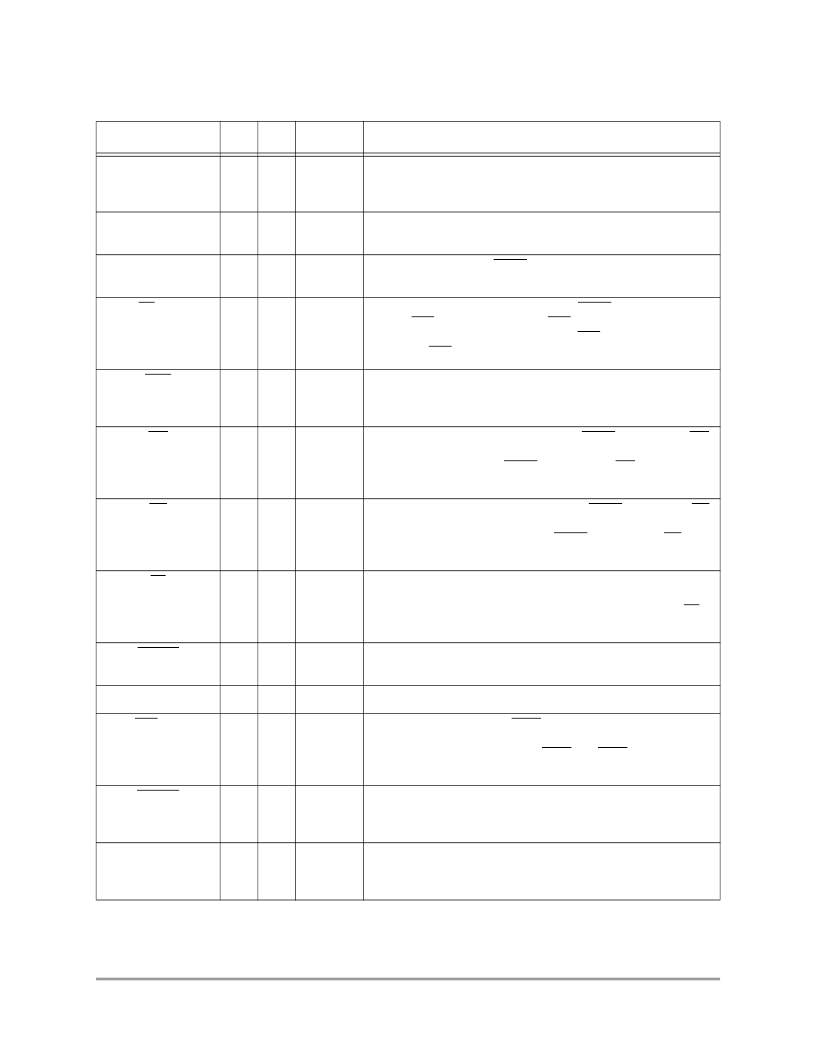

Table 8. External System Bus Signals

Signal Name

Dir

N

I/O Cell

Description

MPD[7:0]/D[15:8]

I/O

Y

IOHPPH

High-Order Data Bus

—

May be used as general I/O when the

data bus is configured as an 8-bit bus. Output drivers are

disabled and pull-up resistors are enabled during reset.

D[7:0]

I/O

Y

IOHPPH

Low-Order Data Bus

—

Output drivers are disabled and pull-up

resistors are enabled during reset.

A[21:0]

I/O

Y

IOHP

Address

—

Input when BGNT is low; otherwise output. Twenty-

two bits is a 4 Mbyte address space.

EB[1:0]

I/O

Y

IOHP

Byte Enable

(active low)

—

Input when BGNT is low; otherwise

output. EB0 enables D[15:8] and EB1 enables D[7:0]. When the

data bus is configured as an 8-bit bus, EB0 is always released

(high) and EB1 is always asserted (low).

BW8

I/O

Y

IOHPPH

Bus Width 8

(open-drain, active low)

—

If this pin is driven low

either externally or internally, the external bus functions as an 8-

bit bus.

WE

I/O

Y

IOHP

Write Enable

(active low)

—

Input when BGNT is low. When WE

is low, data is driven by an external device and received by the

MMC2080. Output when BGNT is high. When WE is low, data is

driven by the MMC2080 and received by an external device.

OE

I/O

Y

IOHP

Output Enable

(active low)

—

Input when BGNT is low; when OE

is high, D[7:0] (and D[15:8] when in 16-bit mode) external data

drivers are disabled. Output when BGNT is high; when OE is

high, drivers are disabled.

TA

O

Y

OTP

Transfer Acknowledge

(active low)

—

An external transaction

continues when this pin is high. When low, the external data

transfer cycle will complete. When MONITOR mode is set. TA

also indicates the end of internal transactions.

ABORT

O

Y

OTP

Data Transfer Abort

(active low)

—

When a transaction is

aborted, this pin is driven low.

BUSCLK

O

Y

OTP

External Bus Clock

.

SEL[3:0]

O

Y

OTP

External Device Select

—

SEL0 is always active low; SEL[3:1]

may be individually programmed as active low or active high.

After reset, SEL3 is active high. SEL1 and SEL2 are active low

after restart.

XBOOT

I

Y

INHPP

External Boot

(active low)

—

If this pin is low after a reset, the

external boot portion of the system memory map is enabled;

otherwise the internal boot map is enabled.

IRQ

O

Y

OTP

Interrupt Request

—

This is driven high when either a normal

interrupt or a fast interrupt is generated by the interrupt

controller.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MMC2075VF001 | Integrated Processor with Roaming FLEX Decoder |

| MMC2080 | Integrated Processor with Roaming FLEX Decoder |

| MMC2080VF001 | Integrated Processor with Roaming FLEX Decoder |

| MMC2107 | HCMOS Microcontroller Unit |

| MMC2107PU | HCMOS Microcontroller Unit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MMC2075VF001 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor with Roaming FLEX Decoder |

| MMC2080 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor with Roaming FLEX Decoder |

| MMC2080VF001 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor with Roaming FLEX Decoder |

| MMC-2102 | 制造商:Pan Pacific 功能描述: |

| MMC2107 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HCMOS Microcontroller Unit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。