- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382335 > MM54HC194 (National Semiconductor Corporation) 4-Bit Bidirectional Universal Shift Register PDF資料下載

參數(shù)資料

| 型號: | MM54HC194 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | 4-Bit Bidirectional Universal Shift Register |

| 中文描述: | 4位雙向通用移位寄存器 |

| 文件頁數(shù): | 1/6頁 |

| 文件大小: | 135K |

| 代理商: | MM54HC194 |

TL/F/5323

M

November 1995

MM54HC194/MM74HC194

4-Bit Bidirectional Universal Shift Register

General Description

This 4-bit high speed bidirectional shift register utilizes ad-

vanced silicon-gate CMOS technology to achieve the low

power consumption and high noise immunity of standard

CMOS integrated circuits, along with the ability to drive 10

LS-TTL loads. This device operates at speeds similar to the

equivalent low power Schottky part.

This bidirectional shift register is designed to incorporate

virtually all of the features a system designer may want in a

shift register. It features parallel inputs, parallel outputs,

right shift and left shift serial inputs, operating mode control

inputs, and a direct overriding clear line. The register has

four distinct modes of operation: PARALLEL (broadside)

LOAD; SHIFT RIGHT (in the direction Q

A

toward Q

D

);

SHIFT LEFT; INHIBIT CLOCK (do nothing).

Synchronous parallel loading is accomplished by applying

the four bits of data and taking both mode control inputs, S0

and S1, high. The data are loaded into their respective flip

flops and appear at the outputs after the positive transition

of the CLOCK input. During loading, serial data flow is inhib-

ited. Shift right is accomplished synchronously with the ris-

ing edge of the clock pulse when S0 is high and S1 is low.

Serial data for this mode is entered at the SHIFT RIGHT

data input. When S0 is low and S1 is high, data shifts left

synchronously and new data is entered at the SHIFT LEFT

serial input. Clocking of the flip flops is inhibited when both

mode control inputs are low. The mode control inputs

should be changed only when the CLOCK input is high.

The 54HC/74HC logic family is functionally as well as pin-

out compatible with the standard 54LS/74LS logic family.

All inputs are protected from damage due to static dis-

charge by internal diode clamps to V

CC

and ground.

Features

Y

Typical operating frequency: 45 MHz

Y

Typical propagation delay: ns (clock to Q)

Y

Wide operating supply voltage range: 2–6V

Y

Low input current: 1

m

A maximum

quiescent

(74HC Series)

Y

Low

supply

current:

160

m

A

maximum

Y

Fanout of 10 LS-TTL loads

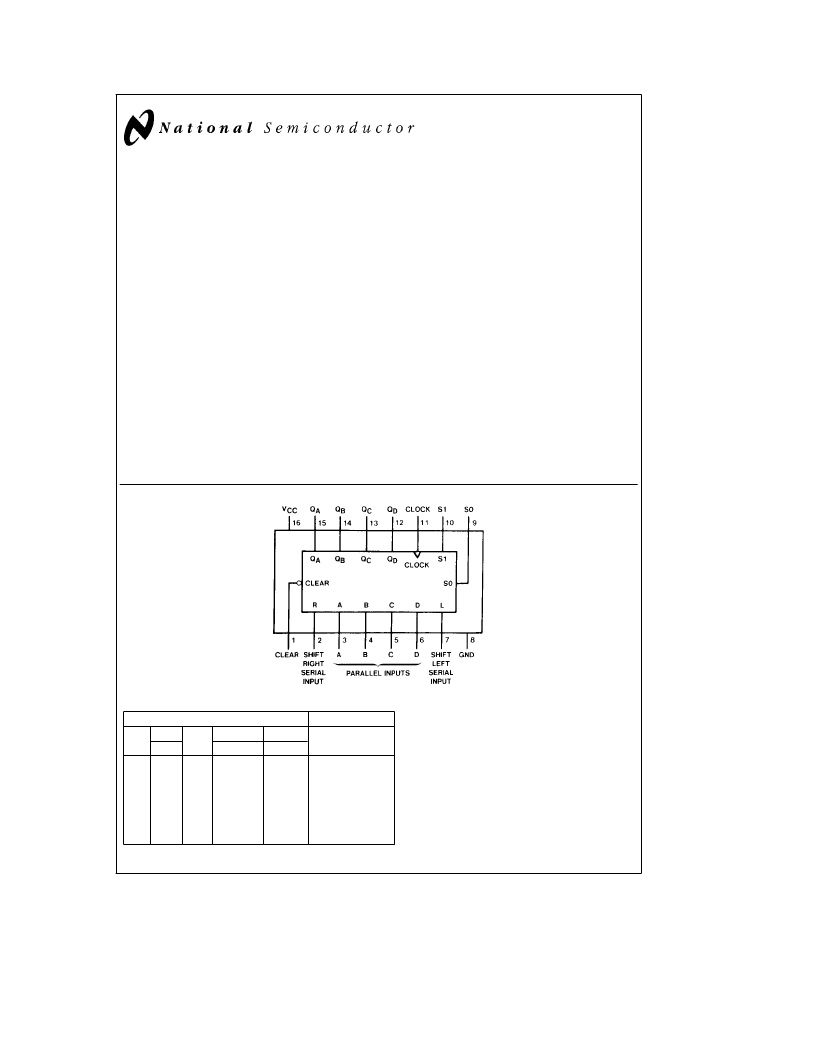

Connection Diagram

Dual-In Line Package

TL/F/5323–1

Order Number MM54HC194 or MM74HC194

Function Table

Inputs

Outputs

Mode

Serial

Parallel

ClearS1 S2ClockLeft Right A B C D

Q

A

Q

B

Q

C

Q

D

L

H

H

H

H

H

H

H

X

X

H

L

L

H

H

L

X

X

H

u

H

u

H

u

L

u

L

u

L

X

L

X

X

X

X

X

H

L

X

X

X

X

H

L

X

X

X

X X X X

X X X X Q

A0

Q

B0

Q

C0

Q

D0

a b c d

a

X X X X

H

X X X X

L

X X X X Q

Bn

Q

Cn

Q

Dn

X X X X Q

Bn

Q

Cn

Q

Dn

X X X X Q

A0

Q

B0

Q

C0

Q

D0

L

L

L

L

b

c

d

Q

An

Q

Bn

Q

Cn

Q

An

Q

Bn

Q

Cn

H

L

X

H

e

high level (steady state)

L

e

low level (steady state)

X

e

irrelevant (any input, including transitions)

u

e

transition from low to high level

a, b, c, d

e

the level of steady-state input at inputs A, B, C, or D,

respectively.

Q

A0

, Q

B0

, Q

C0

, Q

D0

e

the level of Q

A

, Q

B

, Q

C

, or Q

D

, respectively,

before the indicated steady-state input conditions were established.

Q

An

, Q

Bn

, Q

Cn

, Q

Dn

e

the level of Q

A

, Q

B

, Q

C

, respectively, before

the most-recent

u

transition of the clock.

C

1995 National Semiconductor Corporation

RRD-B30M115/Printed in U. S. A.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MM54HC194J | 4-Bit Bidirectional Universal Shift Register |

| MM74HC20 | Zener Diode 225 mW 36 V ±5%SOT-23; Package: SOT-23 (TO-236) 3 LEAD; No of Pins: 3; Container: Tape and Reel; Qty per Container: 3000 |

| MM54HC20 | Dual 4-Input NAND Gate |

| MM54HC20J | Dual 4-Input NAND Gate |

| MM54HC20N | Dual 4-Input NAND Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MM54HC194 WAF | 制造商:Texas Instruments 功能描述: |

| MM54HC194J | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:4-Bit Bidirectional Universal Shift Register |

| MM54HC194J/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MM54HC195 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:4-Bit Parallel Shift Register |

| MM54HC195J | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:4-Bit Parallel Shift Register |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。