- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382331 > MM54C93J (NATIONAL SEMICONDUCTOR CORP) 4-Bit Decade, Binary Counter PDF資料下載

參數(shù)資料

| 型號: | MM54C93J |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | 4-Bit Decade, Binary Counter |

| 中文描述: | CMOS SERIES, ASYN NEGATIVE EDGE TRIGGERED 3-BIT UP BINARY COUNTER, CDIP14 |

| 封裝: | CERAMIC, DIP-14 |

| 文件頁數(shù): | 3/6頁 |

| 文件大小: | 124K |

| 代理商: | MM54C93J |

AC Electrical Characteristics

*

T

A

e

25

§

C, C

L

e

50 pF, unless otherwise specified (Continued)

Symbol

Parameter

Conditions

V

CC

e

5V

V

CC

e

10

V

CC

e

5V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

Min

Typ

Max

Units

t

pd0

, t

pd1

Propagation Delay Time

from A

IN

to Q

C

(MM54C93/MM74C93)

Propagation Delay Time from

A

IN

to Q

C

(MM54C93/MM74C93)

Propagation Delay Time from

A

IN

to Q

D

(MM54C93/MM74C93)

Propagation Delay Time from

A

IN

to Q

D

(MM54C90/MM74C90)

Propagation Delay Time from

R

01

or R

02

to Q

A

, Q

B

, Q

C

or Q

D

(MM54C93/MM74C93)

500

200

1050

400

ns

ns

t

pd0

, t

pd1

500

200

1000

400

ns

ns

t

pd0

, t

pd1

600

250

1200

500

ns

ns

t

pd0

, t

pd1

450

160

800

300

ns

ns

t

pd0

, t

pd1

150

75

300

150

ns

ns

t

pd0

, t

pd1

Propagation Delay Time from

R

01

or R

02

to Q

A

, Q

B

, Q

C

or Q

D

(MM54C90/MM74C90)

V

CC

e

5V

V

CC

e

10V

200

75

400

150

ns

ns

t

pd0

, t

pd1

Propagation Delay Time from

R

91

or R

92

to Q

A

or Q

D

(MM54C90/MM74C90)

V

CC

e

5V

V

CC

e

10V

250

100

500

200

ns

ns

t

PW

Min. R

01

or R

02

Pulse Width

(MM54C93/MM74C93)

V

CC

e

5V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

V

CC

e

10V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

V

CC

e

5V

V

CC

e

10V

Any Input (Note 2)

600

30

250

125

ns

ns

t

PW

Min. R

01

or R

02

Pulse Width

(MM54C90/MM74C90)

600

300

250

125

ns

ns

t

PW

Min. R

91

or R

92

Pulse Width

(MM54C90/MM74C90)

500

250

200

100

ns

ns

t

r

, t

f

Maximum Clock Rise

and Fall Time

15

5

m

s

m

s

t

W

Minimum Clock Pulse Width

250

100

100

50

ns

ns

f

MAX

Maximum Clock Frequency

2

5

MHz

MHz

C

IN

C

PD

*

AC Parameters are guaranteed by DC correlated testing.

Input Capacitance

5

pF

Power Dissipation Capacitance

Per Package (Note 3)

45

pF

Note 1:

‘‘Absolute Maximum Ratings’’ are those values beyond which the safety of the device cannot be guaranteed. Except for ‘‘Operating Temperature Range’’,

they are not meant to imply that the devices should be operated at these limits. The table of ‘‘Electrical Characteristics’’ provides conditions for actual device

operation.

Note 2:

Capacitance is guaranteed by periodic testing.

Note 3:

C

PD

determines the no load ac power consumption of any CMOS device. For complete explanation see 54C/74C Family Characteristics application noteD

AN-90.

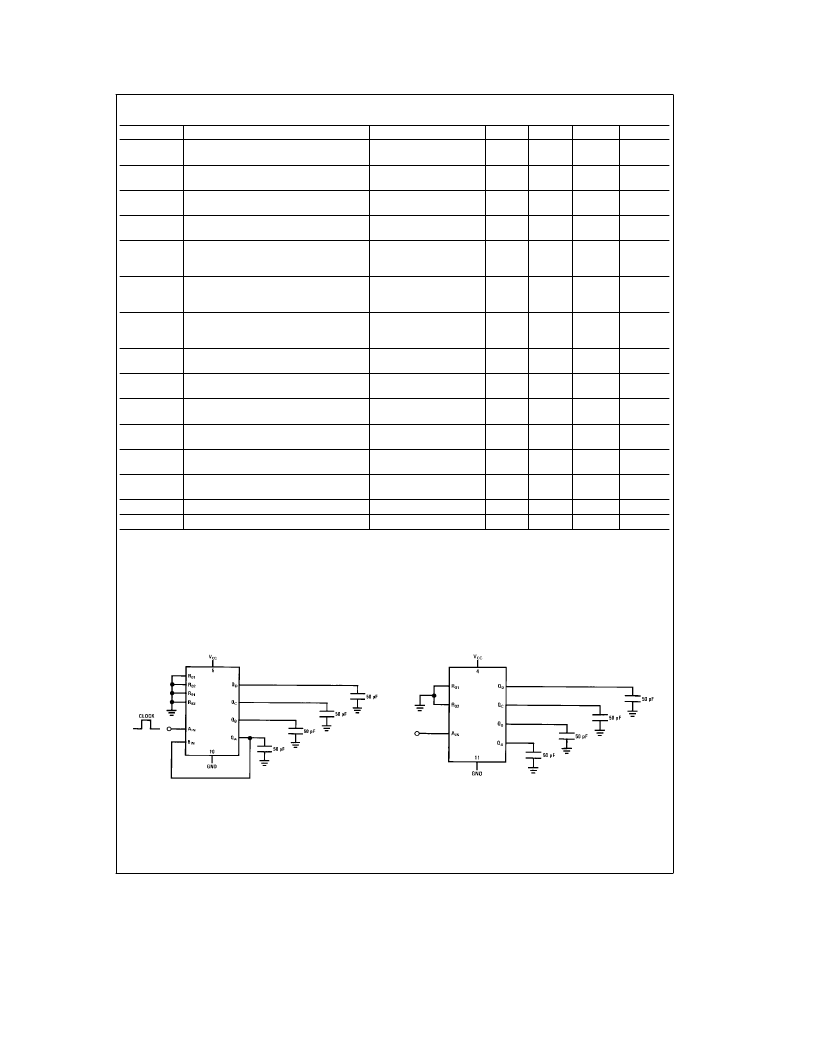

AC Test Circuits

MM54C90/MM74C90

TL/F/5889–5

Clock rise and fall time t

r

e

t

f

e

20 ns

MM54C93/MM74C93

TL/F/5889–6

Clock rise and fall time t

r

e

t

f

e

20 ns

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MM54C93N | 4-Bit Decade, Binary Counter |

| MM54C932 | Phase Comparator |

| MM54C932N | Phase Comparator |

| MM74C932 | Phase Comparator |

| MM74C932N | Phase Comparator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MM54C93N | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:4-Bit Decade, Binary Counter |

| MM54C941 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Buffers/Line Receivers/ Line Drivers with TRI-STATE Outputs |

| MM54C941J | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Buffers/Line Receivers/ Line Drivers with TRI-STATE Outputs |

| MM54C941N | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Buffers/Line Receivers/ Line Drivers with TRI-STATE Outputs |

| MM54C95 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:4-Bit Right-Shift Left-Shift Register |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。