- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98021 > MJE5852BG (ON SEMICONDUCTOR) 8 A, 400 V, PNP, Si, POWER TRANSISTOR PDF資料下載

參數(shù)資料

| 型號(hào): | MJE5852BG |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 功率晶體管 |

| 英文描述: | 8 A, 400 V, PNP, Si, POWER TRANSISTOR |

| 封裝: | PLASTIC, TO-220AB, 3 PIN |

| 文件頁(yè)數(shù): | 14/63頁(yè) |

| 文件大小: | 445K |

| 代理商: | MJE5852BG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)

Surface Mount Package Information and Tape and Reel Specifications

4–2

Motorola Bipolar Power Transistor Device Data

INFORMATION FOR USING SURFACE MOUNT PACKAGES

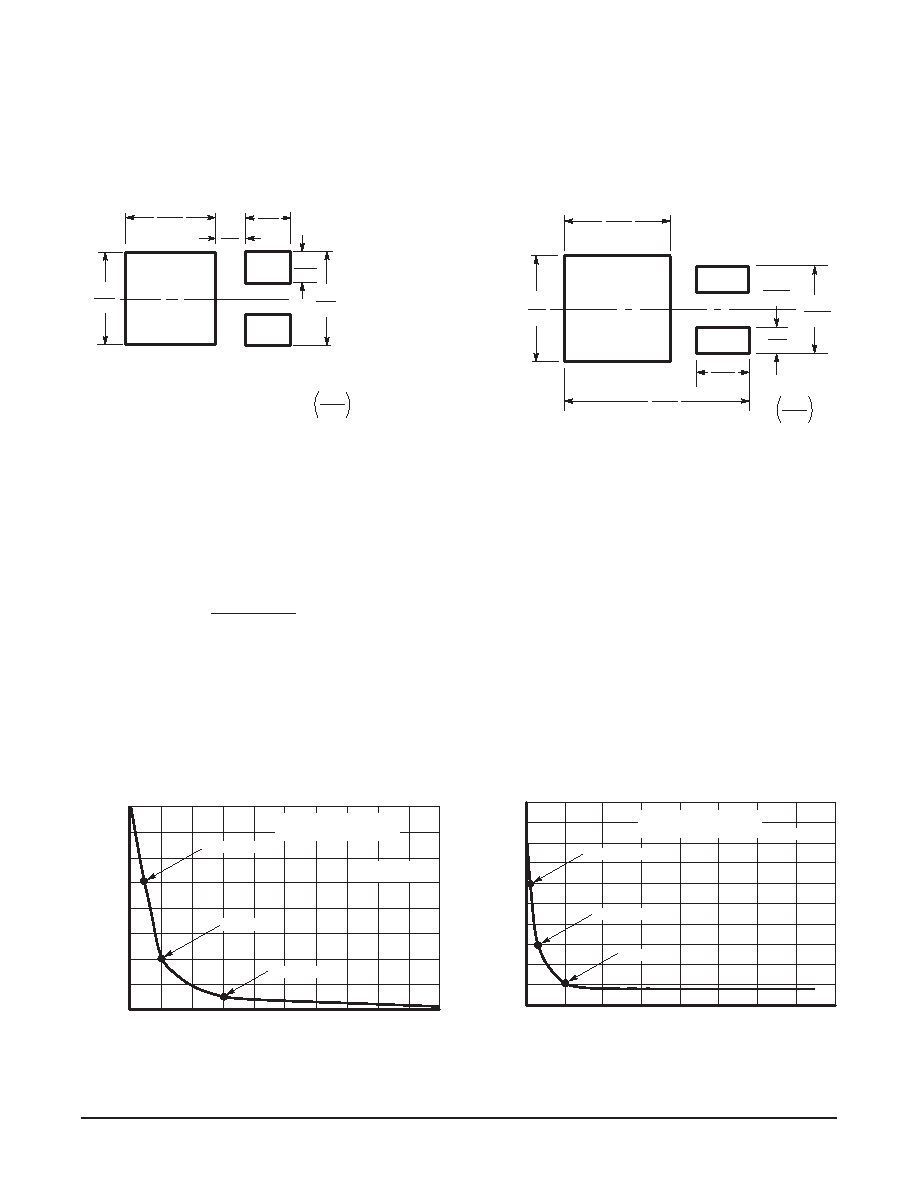

RECOMMENDED FOOTPRINTS FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total

design. The footprint for the semiconductor packages must

be the correct size to ensure proper solder connection inter-

face between the board and the package. With the correct

pad geometry, the packages will self align when subjected to

a solder reflow process.

POWER DISSIPATION FOR A SURFACE MOUNT DEVICE

The values for the equation are found in the maximum

ratings table on the data sheet. Substituting these values into

the equation for an ambient temperature TA of 25°C, one can

calculate the power dissipation of the device. For example,

for a D2PAK, PD is calculated as follows.

PD =

150

°C – 25°C

50

°C/W

= 2.5 watts

The 50

°C/W for the D2PAK package assumes the use of

the recommended footprint on a glass epoxy printed circuit

board to achieve a power dissipation of 2.5 watts. There are

other alternatives to achieving higher power dissipation from

the surface mount packages. One is to increase the area of

the drain/collector pad. By increasing the area of the drain/

collector pad, the power dissipation can be increased.

Although the power dissipation can almost be doubled with

this method, area is taken up on the printed circuit board

which can defeat the purpose of using surface mount

technology. For example, a graph of R

θJA versus drain pad

area is shown in Figures 1 and 2.

Another alternative would be to use a ceramic substrate or

an aluminum core board such as Thermal Clad

. Using a

board material such as Thermal Clad, an aluminum core

board, the power dissipation can be doubled using the same

footprint.

DPAK

0.19

0

4.82

6

mm

inches

0.10

0

2.54

0.063

1.6

0.165

4.191

0.118

3.0

0.243

6.172

D2PAK

mm

inches

0.33

8.38

0.08

2.032

0.04

1.016

0.63

17.02

0.42

10.6

6

0.1

2

3.0

5

0.24

6.096

1.75 Watts

Board Material = 0.0625

″

G–10/FR–4, 2 oz Copper

80

100

60

40

20

10

8

6

4

2

0

3.0 Watts

5.0 Watts

TA = 25°C

A, AREA (SQUARE INCHES)

T

O

AMBIENT

(

C/W)°

R

JA

,T

HERM

AL

RESIS

TA

NCE,

JUNC

T

ION

θ

Figure 1. Thermal Resistance versus Drain Pad

Area for the DPAK Package (Typical)

Figure 2. Thermal Resistance versus Drain Pad

Area for the D2PAK Package (Typical)

2.5 Watts

A, AREA (SQUARE INCHES)

Board Material = 0.0625

″

G–10/FR–4, 2 oz Copper

TA = 25°C

60

70

50

40

30

20

16

14

12

10

8

6

4

2

0

3.5 Watts

5 Watts

T

O

AMBIENT

(

C/W)°

R

JA

,T

HERM

AL

RESIS

TA

NCE,

JUNC

T

ION

θ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MJE5852BD | 8 A, 400 V, PNP, Si, POWER TRANSISTOR |

| MJE5852AN | 8 A, 400 V, PNP, Si, POWER TRANSISTOR |

| MJE5852AK | 8 A, 400 V, PNP, Si, POWER TRANSISTOR |

| MJE5852AJ | 8 A, 400 V, PNP, Si, POWER TRANSISTOR |

| MJE5851AS | 8 A, 350 V, PNP, Si, POWER TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MJE5852G | 功能描述:兩極晶體管 - BJT 8A 400V 80W PNP RoHS:否 制造商:STMicroelectronics 配置: 晶體管極性:PNP 集電極—基極電壓 VCBO: 集電極—發(fā)射極最大電壓 VCEO:- 40 V 發(fā)射極 - 基極電壓 VEBO:- 6 V 集電極—射極飽和電壓: 最大直流電集電極電流: 增益帶寬產(chǎn)品fT: 直流集電極/Base Gain hfe Min:100 A 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PowerFLAT 2 x 2 |

| MJE6040 | 制造商:NJSEMI 制造商全稱:New Jersey Semi-Conductor Products, Inc. 功能描述:POWER DERATING |

| MJE6041 | 制造商:NJSEMI 制造商全稱:New Jersey Semi-Conductor Products, Inc. 功能描述:POWER DERATING |

| MJE6043 | 制造商:NJSEMI 制造商全稱:New Jersey Semi-Conductor Products, Inc. 功能描述:POWER DERATING |

| MJE6044 | 制造商:NJSEMI 制造商全稱:New Jersey Semi-Conductor Products, Inc. 功能描述:POWER DERATING |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。