- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371108 > MH8S64BBKG-8 (Mitsubishi Electric Corporation) 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM PDF資料下載

參數(shù)資料

| 型號: | MH8S64BBKG-8 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| 中文描述: | 536870912位(8388608 -文字,64位)SynchronousDRAM |

| 文件頁數(shù): | 5/55頁 |

| 文件大小: | 588K |

| 代理商: | MH8S64BBKG-8 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

MH8S64PHC -7,-8,-10

536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM

MITSUBISHI LSIs

( / 55 )

MITSUBISHI

ELECTRIC

9/ Dec. /1998

Preliminary Spec.

Some contents are subject to change without notice.

MIT-DS-0282-0.0

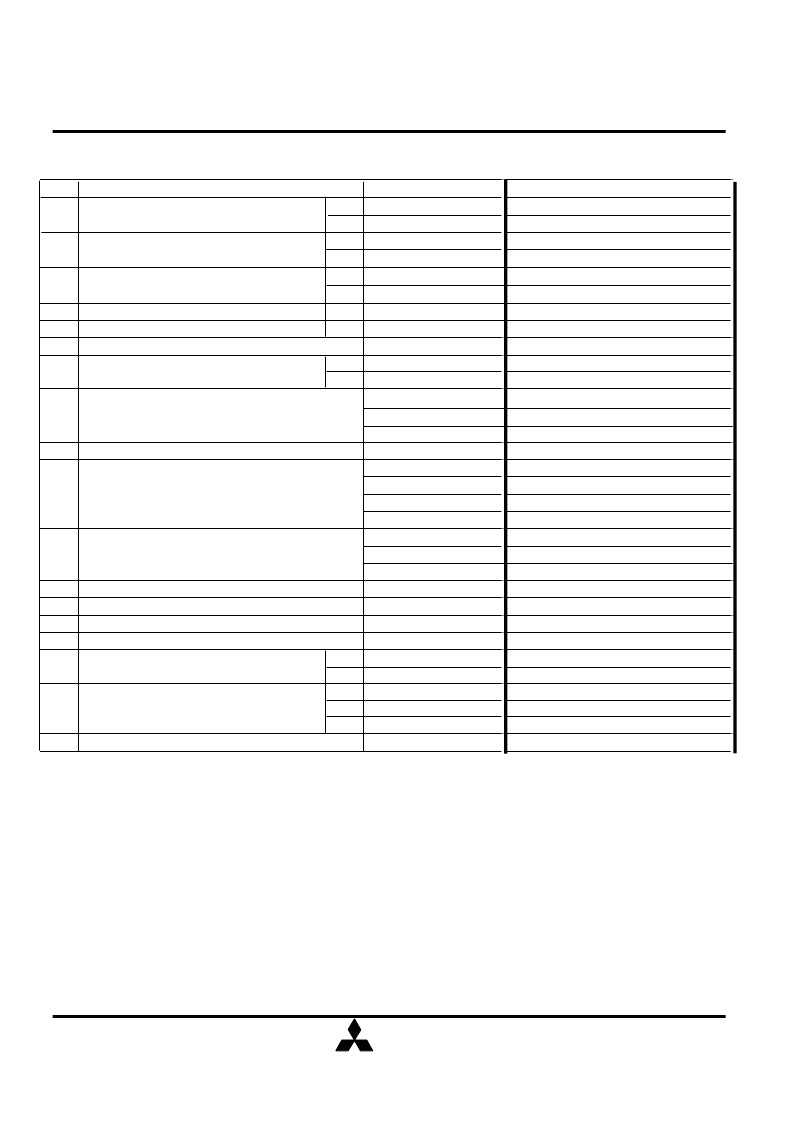

Serial Presence Detect Table II

31

32

Density of each bank on module

Command and Address signal input setup time

64MByte

2ns

N/A

10

20

00

36-61

62

Superset Information (may be used in future)

SPD Revision

option

rev 1.2A

00

12

rev 1

01

63

Checksum for bytes 0-62

Check sum for -8

Check sum for -10

4D

4A

64-71

72

Manufactures Jedec ID code per JEP-108E

Manufacturing location

MITSUBISHI

Miyoshi,Japan

Tajima,Japan

NC,USA

Germany

1CFFFFFFFFFFFFFF

01

02

03

04

73-90

Manufactures Part Number

MH8S64PHC-8

MH8S64PHC-10

91-92

93-94

95-98

99-125

126

Revision Code

Manufacturing date

Assembly Serial Number

Manufacture Specific Data

Intetl specification frequency

PCB revision

year/week code

serial number

option

100MHz

66MHz

CL=2/3,AP,CK0,2

CL=3,AP,CK0,2

rrrr

yyww

ssssssss

00

64

66

AF

AD

127

Intel specification CAS# Latency support

06

128+

Unused storage locations

open

00

-7,-8

-10

20

00

33

Command and Address signal input hold time

-7,-8

-10

1ns

N/A

10

00

34

Data signal input setup time

-7,-8

-10

2ns

N/A

1ns

N/A

35

Data signal input hold time

-7,-8

-10

10

00

-7,-8

-10

Check sum for -7

0D

MH8S64PHC-7

4D48385336345048432D3720202020202020

4D48385336345048432D3820202020202020

-7,-8

-10

-7

-10

4D48385336345048432D3130202020202020

CL=2/3

-8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH8S64BBKG-8L | 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64DALD-6 | 536870912-BIT (8388608 - WORD BY 64-BIT)Synchronous DRAM |

| MH8S64DALD-7 | 536870912-BIT (8388608 - WORD BY 64-BIT)Synchronous DRAM |

| MH8S64DALD-8 | 536870912-BIT (8388608 - WORD BY 64-BIT)Synchronous DRAM |

| MH8S64DBKG-6 | 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH8S64BBKG-8L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64BMG-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64BMG-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64BMG-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64DALD-6 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。